8.2.1 时钟信号描述

众所周知,在时序逻辑电路中,驱动信号就是时钟信号,时序逻辑电路只是在时钟信号边沿到来时,它的状态才会发生改变。因此,在时序逻辑电路中时钟信号是非常重要的,它是时序逻辑电路的执行条件和同步信号。

由于时钟在时序逻辑电路中的重要性,因此在用VHDL描述时序逻辑电路的时候,时钟信号的描述就显得十分重要。时序逻辑电路常常采用时钟进程的形式来进行描述,也就是说,在时序逻辑电路中进程的敏感信号是时钟信号。

1.时钟作为敏感信号的描述方式

在用VHDL描述时序逻辑电路的时候,时钟作为敏感信号的描述方式有两种:在进程的敏感信号表中列出或在WAIT语句中描述。

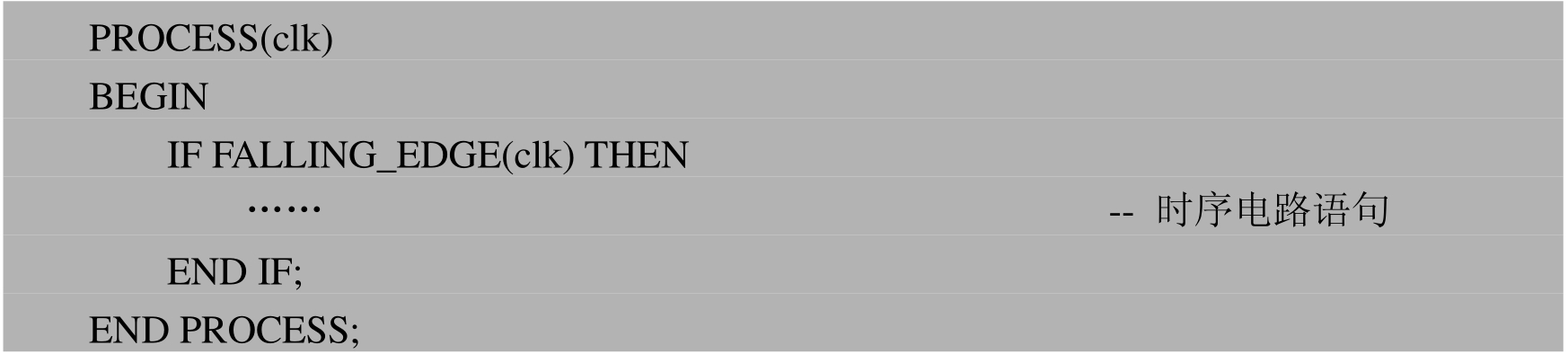

(1)时钟信号直接在进程的敏感信号表中列出

在这种情况下,时钟信号应作为敏感信号,显式地出现在PROCESS语句后面的敏感信号表括号中,如例8-1所示出现在PROCESS语句后面的敏感信号表括号中。

【例8-1】时钟信号在进程的敏感信号表中列出

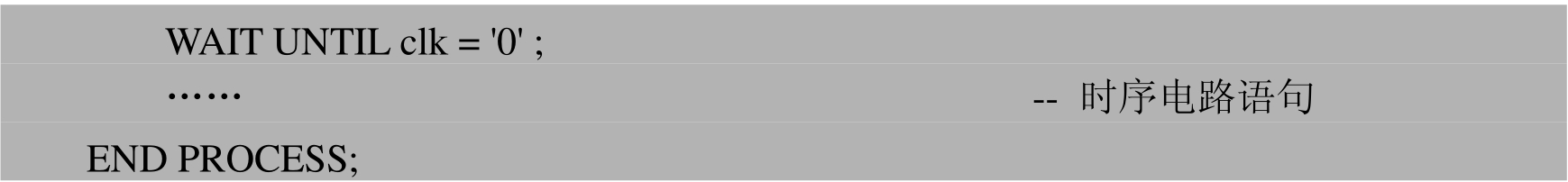

(2)时钟信号在WAIT语句中描述,在进程的敏感信号表中不列出

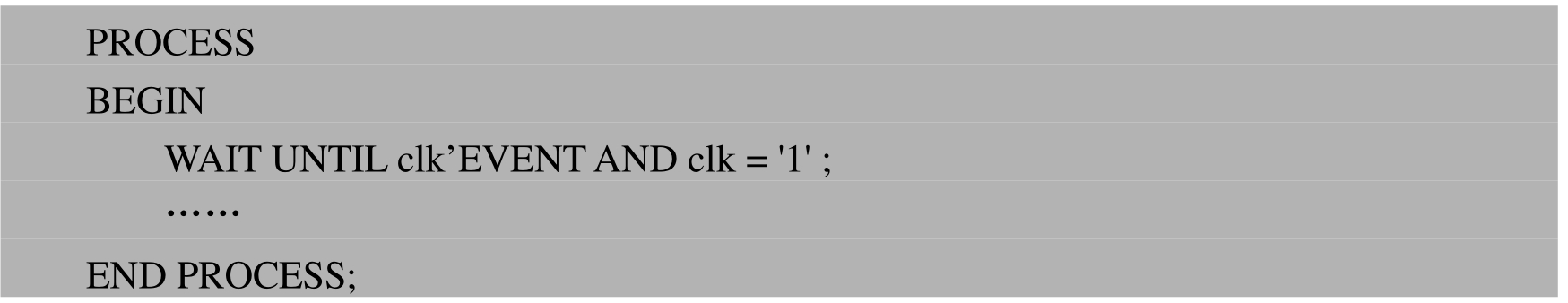

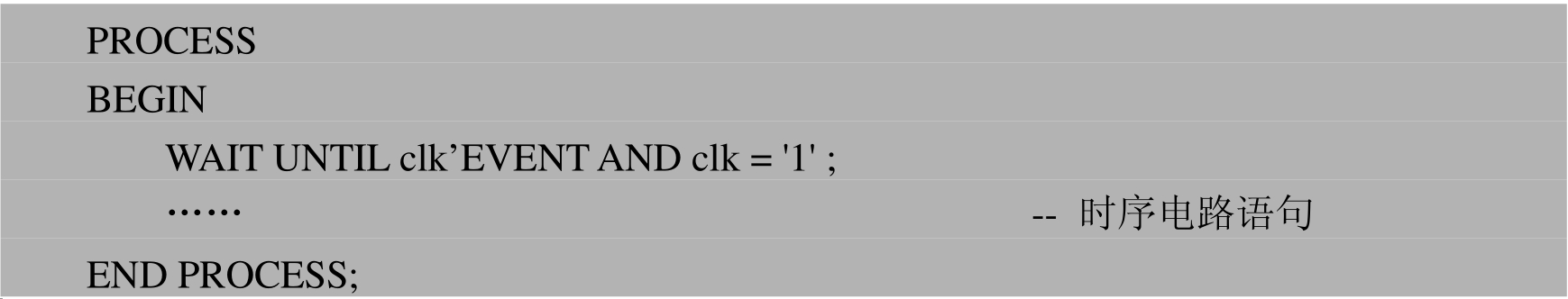

在这种情况下,描述时序电路的进程将没有敏感信号表,而是用WAIT语句来控制进程的执行。也就是说,进程通常停留在WAIT语句上,只有在时钟信号到来,且满足边沿条件时,进程才继续往下执行。例8-2给出了WAIT语句带时钟的几种描述方式。

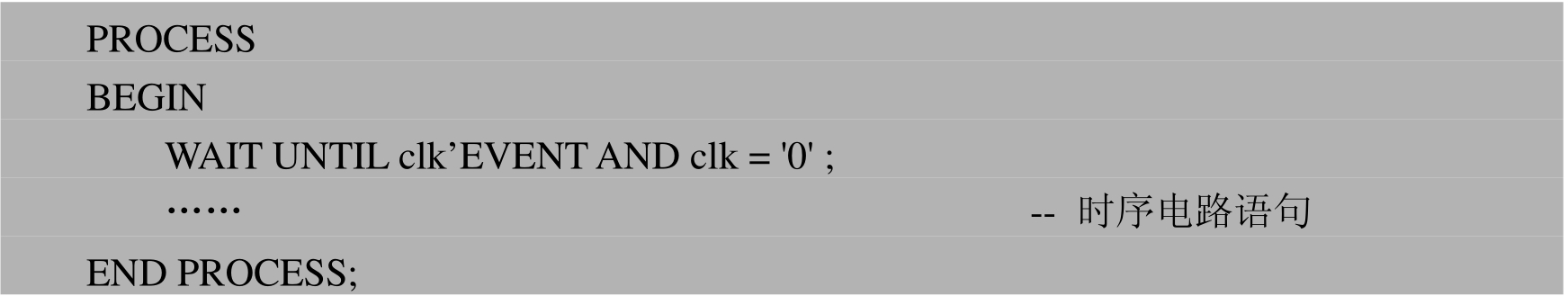

【例8-2】时钟信号在WAIT语句中的描述描述方式1:

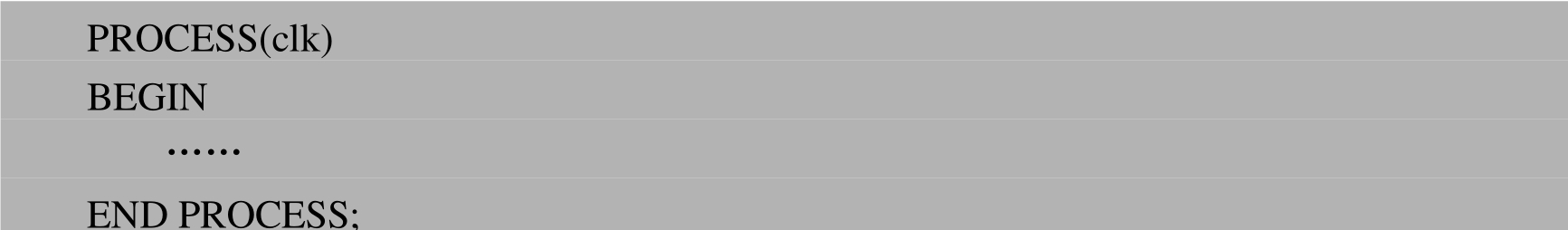

描述方式2:

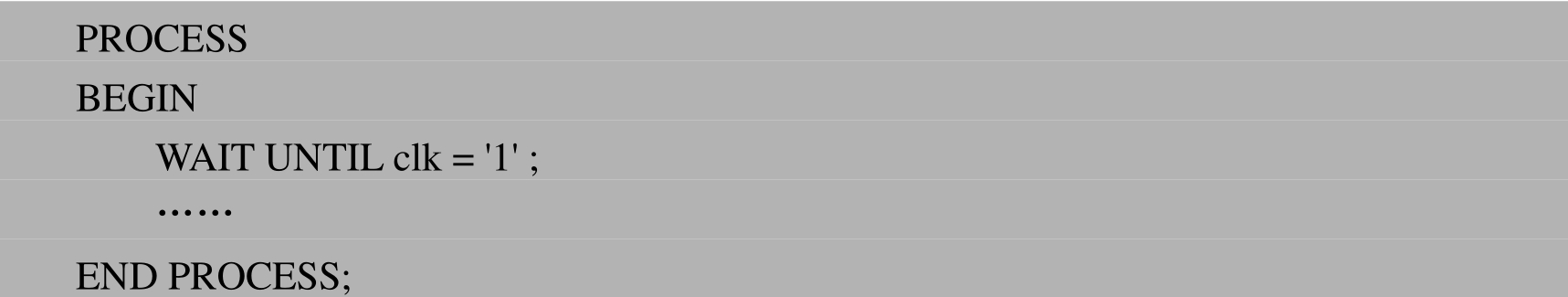

描述方式3:

2.时钟边沿的描述

在时序逻辑电路中,时钟是采用边沿来触发的,因此VHDL对时钟边沿的描述就非常重要。时钟边沿的描述通常采用VHDL中的预定义属性来完成。时钟边沿分为上升沿和下降沿。

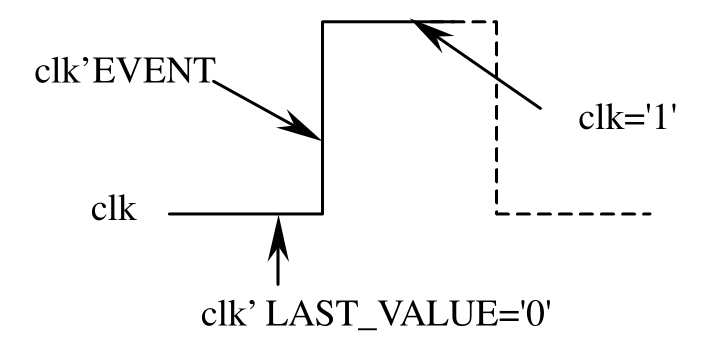

(1)时钟的上升沿描述

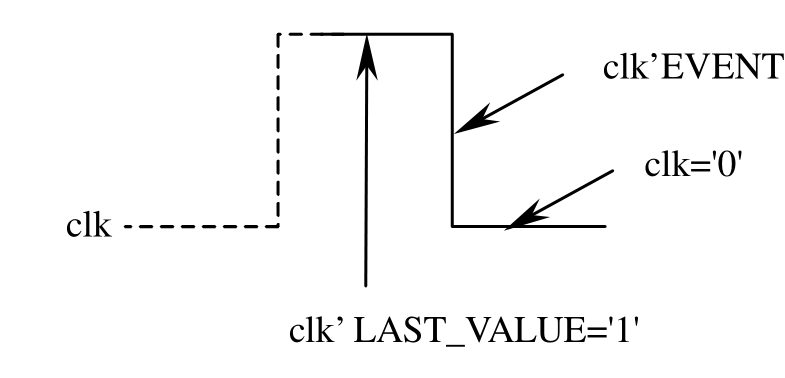

时钟上升沿的物理意义是指时钟信号的逻辑从“0”变到“1”。时钟上升沿波形与时钟信号属性的描述关系如图8.1所示。

图8.1 时钟上升沿及其属性

从图8.1中可以看到,时钟信号起始值为“0”,故其属性值clk’LAST_VALUE='0';上升沿的到来表示发生了一个事件,故用clk’EVENT表示;上升沿以后,时钟信号的值为“1”,故其当前值为clk='1'。于是,表示上升沿到来的条件可写为:

![]()

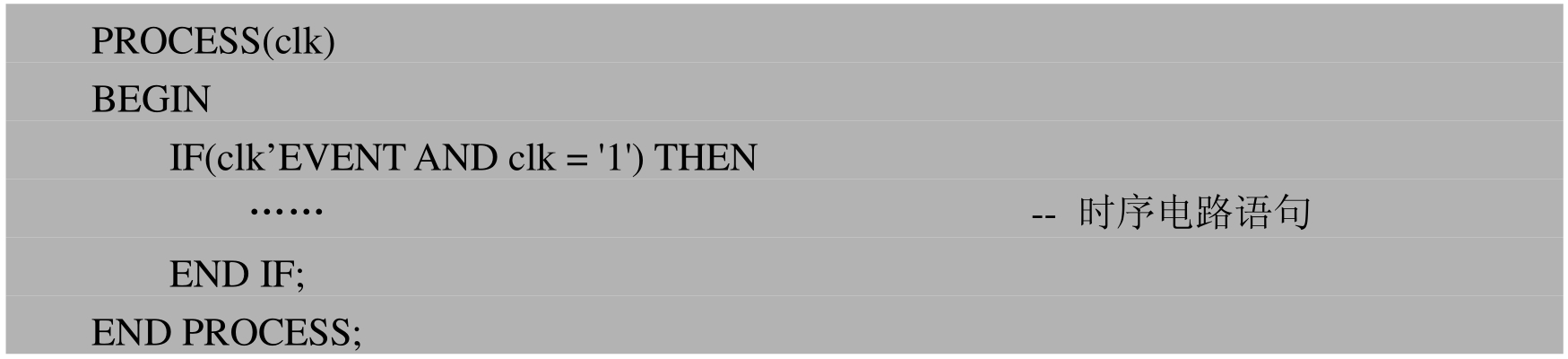

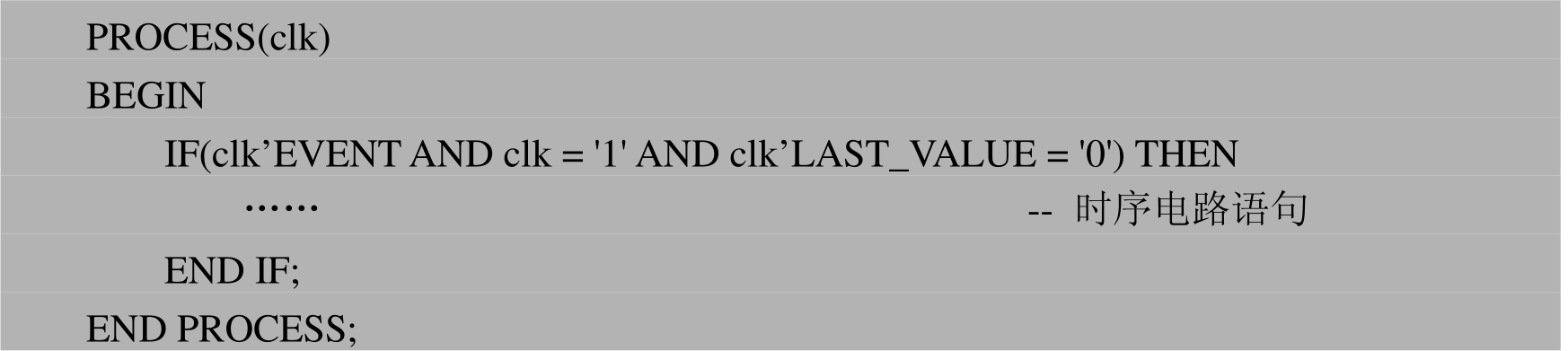

时钟上升沿的描述有多种形式,集中列举如例8-3所示。

【例8-3】时钟上升沿的描述

描述方式1:

描述方式2:

描述方式3:

描述方式4:

描述方式5:

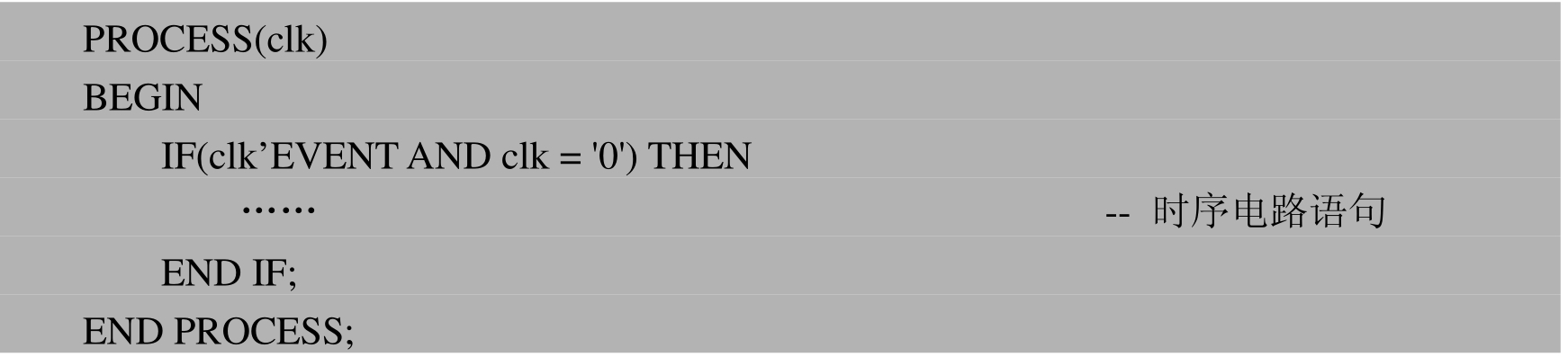

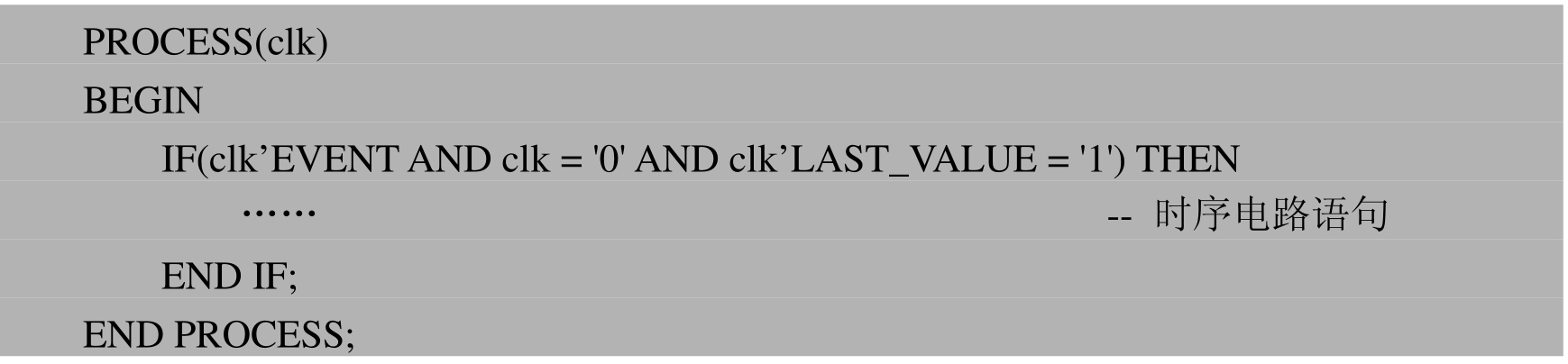

(2)时钟脉冲下降沿描述

时钟下降沿的物理意义是指时钟信号的逻辑从“1”变到“0”。时钟脉冲下降沿波形与时钟信号属性的描述关系如图8.2所示。此时clk’LAST_VALUE='1';时钟信号当前值为clk='0';下降沿到来的事件为clk’EVENT。这样表示下降沿到来的条件可写为:

图8.2 时钟下降沿及其属性

![]()

时钟下降沿的描述同样有多种形式,集中列举如例8-4所示。

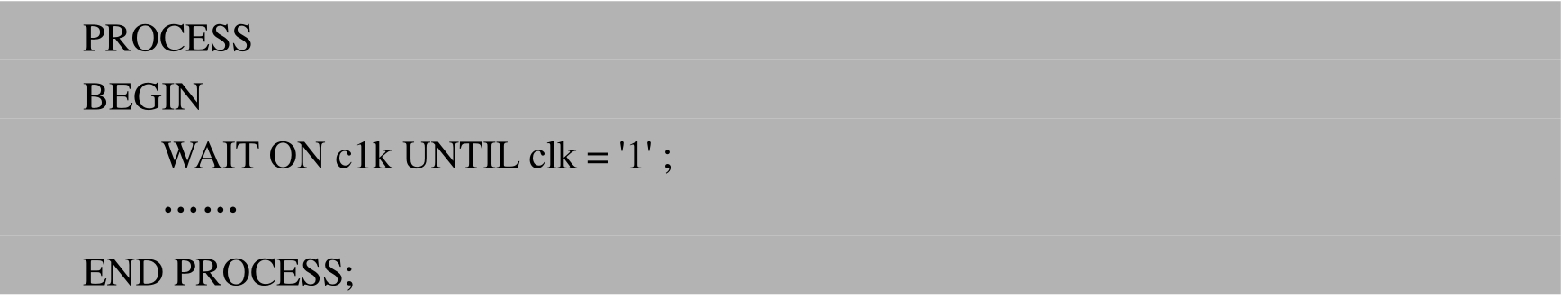

【例8-4】时钟下降沿的描述

描述方式1:

描述方式2:

描述方式3:

描述方式4:

![]()

描述方式5: