D触发器

触发器中最常用的是D触发器,几乎所有的数字逻辑电路都可由D触发器和组合逻辑电路构成。用VHDL描述数字逻辑电路时,VHDL综合器通常将带时钟的触发器都描述成D触发器或D触发器外加组合逻辑电路。

1.一般D触发器

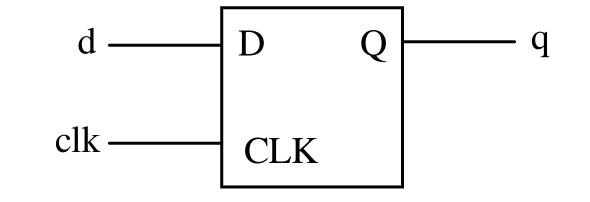

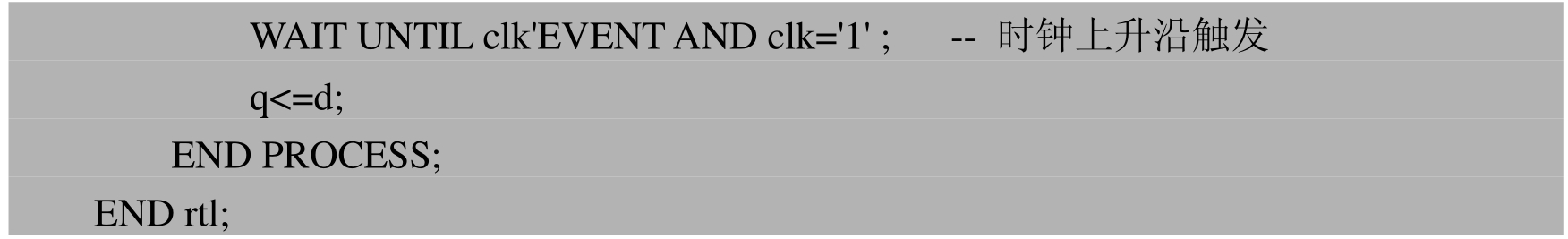

一个基本的D触发器的电路符号如图8.3所示。它是一个上升沿触发的D触发器,有一个数据输入端d,一个时钟输入端clk和一个数据输出端q。D触发器的真值表如表8.1所示。从表中可以看到,D触发器的输出端只有在上升沿脉冲到来时,输入端d的数据才传递到输出端q。用VHDL描述该D触发器的程序如例8-8和例8-9所示。

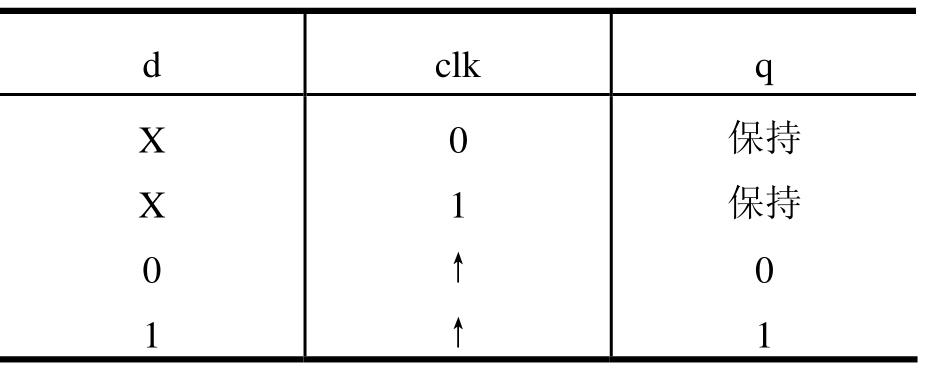

表8.1 D触发器真值表

图8.3 D触发器电路符号图

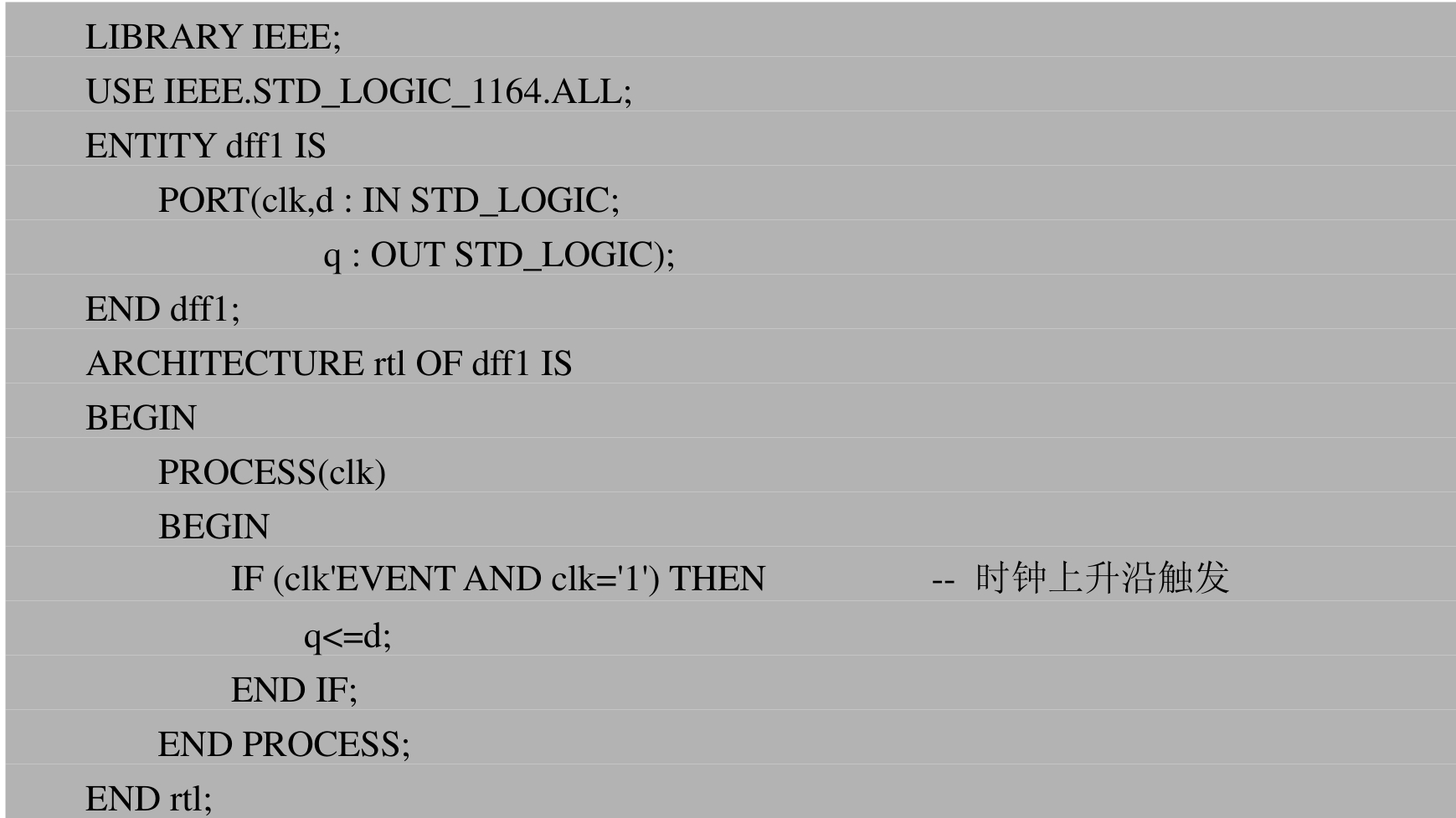

【例8-8】进程带敏感信号表的D触发器

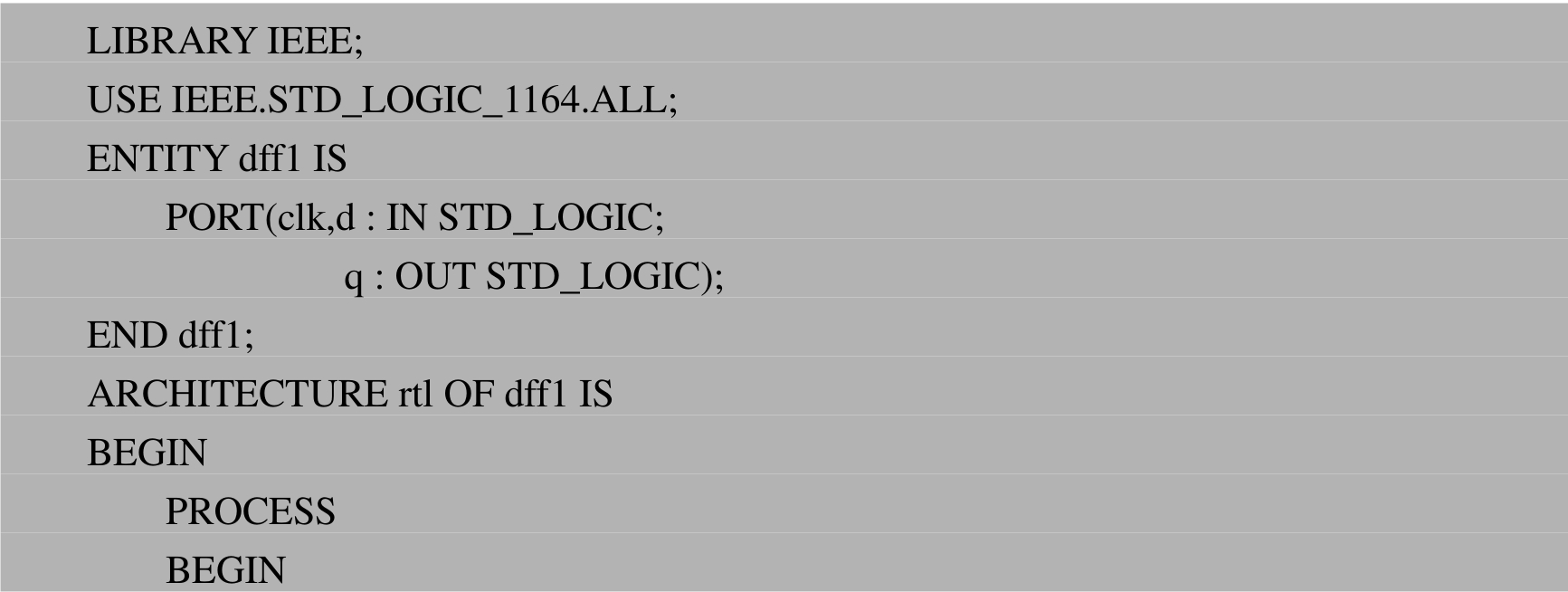

【例8-9】进程带WAIT语句的D触发器

例8-8和例8-9是对时钟信号边沿利用前述的不同方法描述所得到的两个不同的程序。程序中描述的是上升沿触发,如果要描述下降沿触发,只需将条件改成“clk'EVENT AND clk='0'”即可。

2.异步复位D触发器

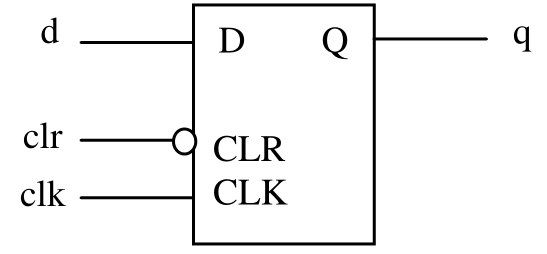

异步复位的D触发器的电路符号如图8.4所示。它和一般D触发器的区别是多了一个复位信号输入端clr。当clr=“0”时,其q端输出被强迫置为“0”。clr又称为清零信号输入端。

用VHDL描述的异步复位D触发器如例8-10所示。

图8.4 异步复位D触发器

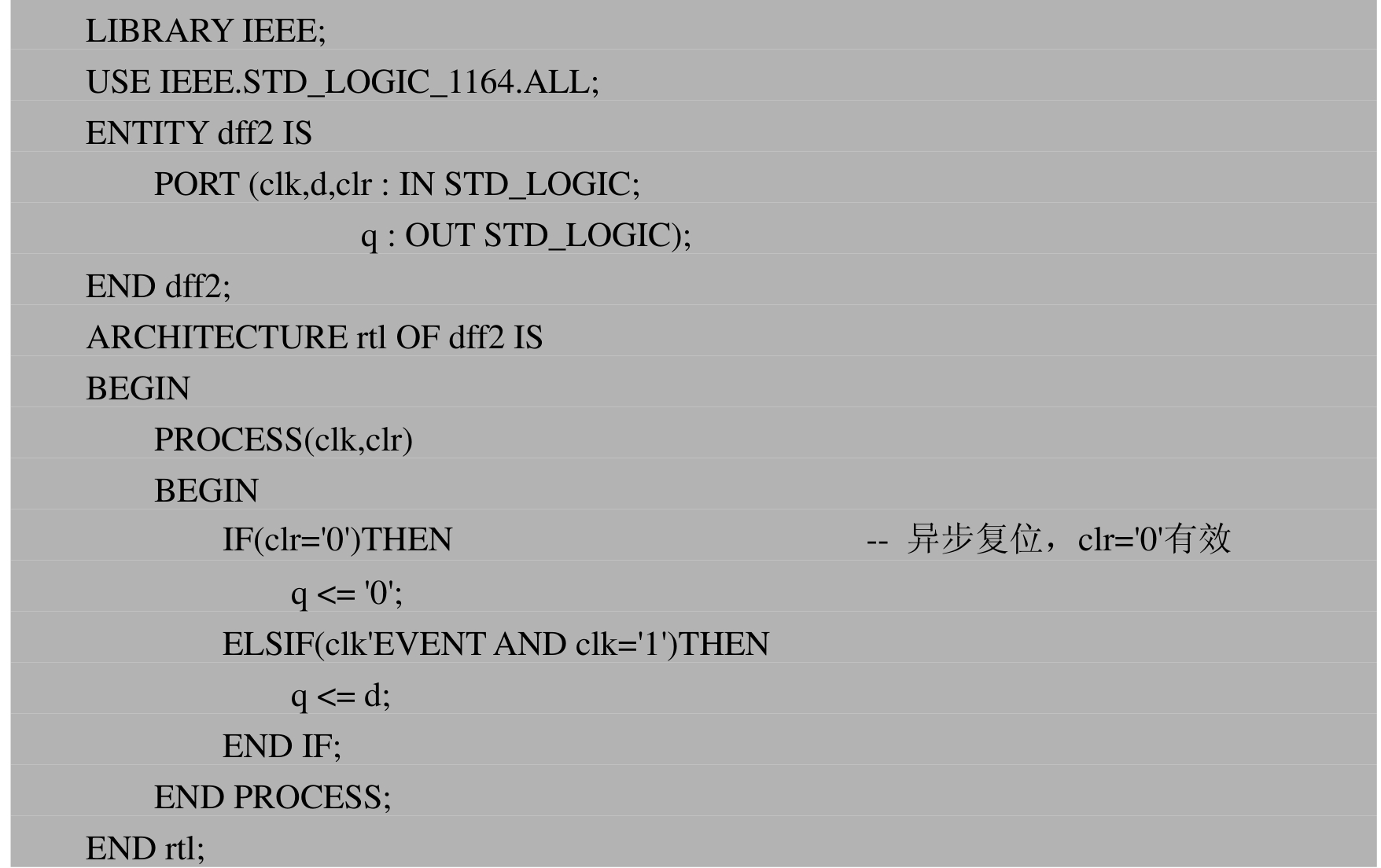

【例8-10】异步复位D触发器

3.异步复位/置位D触发器

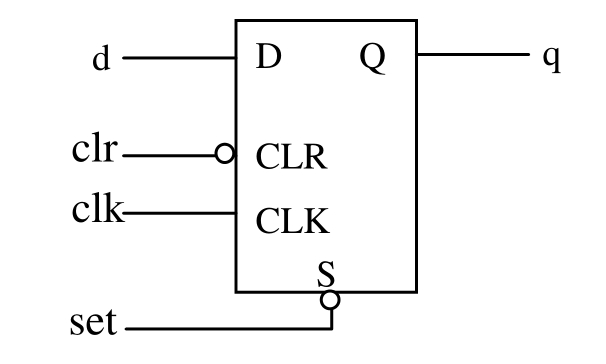

异步复位/置位D触发器的电路符号如图8.5所示。除了前述的d、clk和q端外,还有复位信号clr和置位信号set。当set=“0”时置位,使q=“1”;当clr=“0”时复位,使q=“0”。

用VHDL描述的非同步复位/置位D触发器的程序如例8-11所示。

图8.5 异步复位/置位D触发器

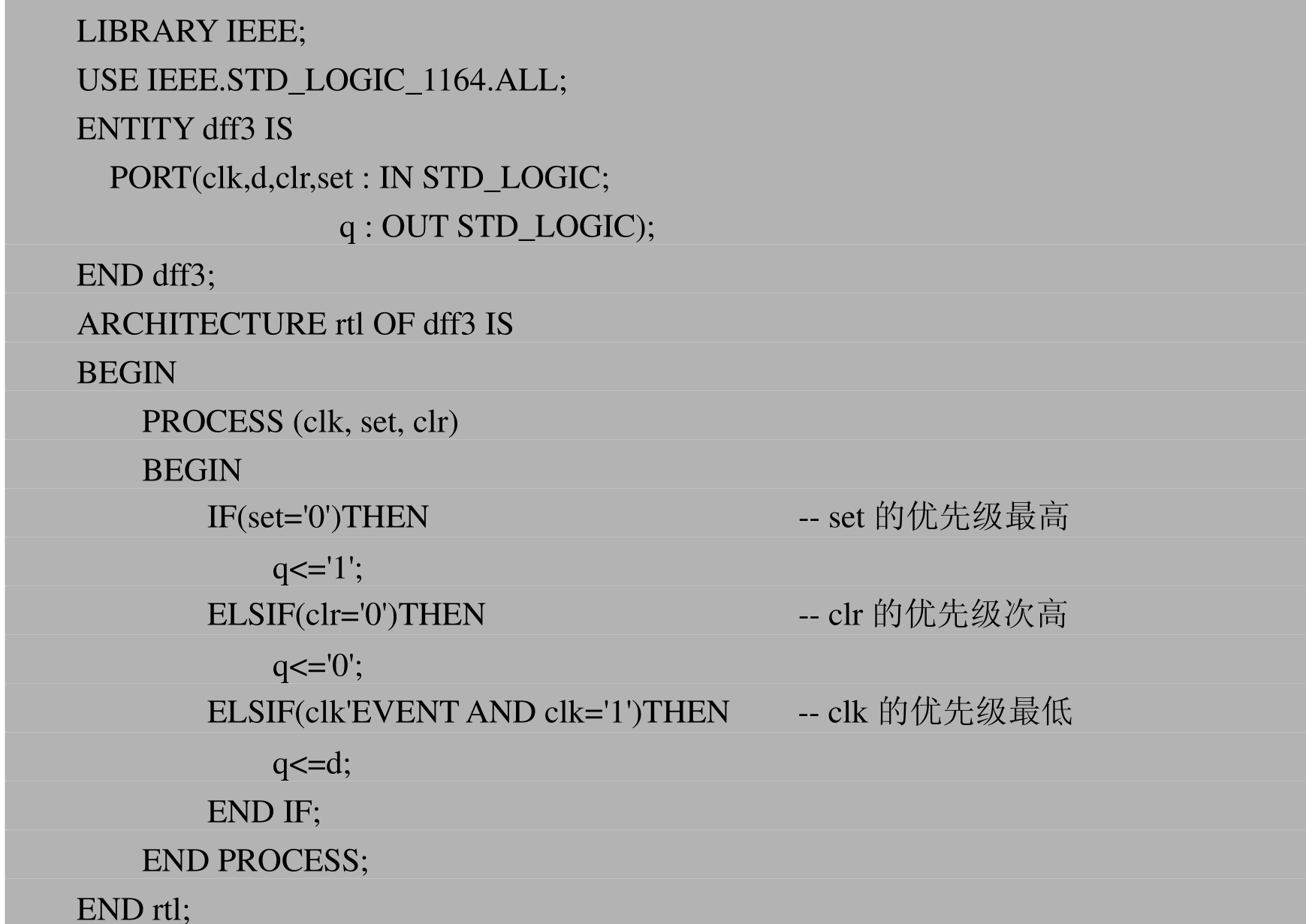

【例8-11】异步复位/置位D触发器

从例8-11可以看到,置位的优先级最高,复位次之,时钟最低,这样,当set=0时,无论clr和clk是什么状态,q一定被置为“1”。

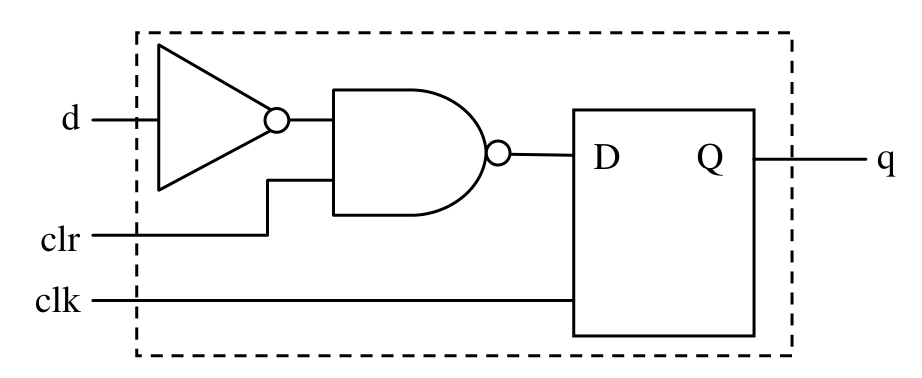

4.同步复位D触发器

同步复位D触发器的逻辑电路如图8.6所示。与异步复位方式不同的是,当复位信号有效(clr=“0”)以后,只是在有效时钟边沿到来时才能进行复位操作。图中c1r=“0”以后,在clk的上升沿到来时,q输出才变为“0”。另外,从图中还可以看出复位信号clr的优先级比数据输入端d高,也就是说当clr=“0”时,无论输入端d是什么信号,在clk的上升沿到来时,q输出总是为“0”。

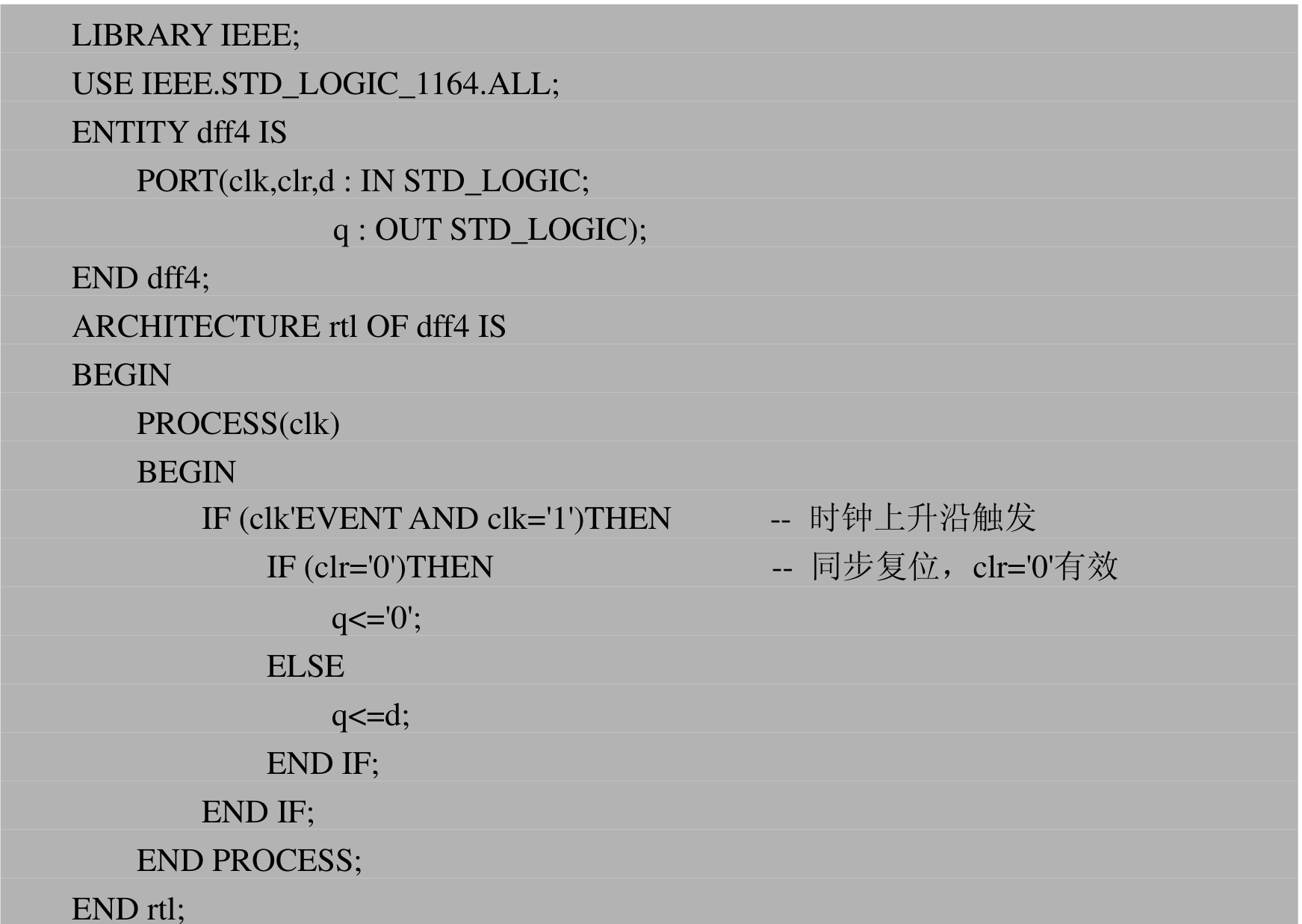

用VHDL描述的同步复位D触发器的程序实例如例8-12所示。

图8.6 同步复位D触发器

【例8-12】同步复位D触发器

上一篇:无论发生什么事,保持一颗平常心

下一篇:外汇交易数据行情公布时间