5.1.2 可编程模拟电路软件介绍

(1)ispPAC的开发软件为PAC-Designer,对计算机的软、硬件配置要求:

①Windows 95、98、NT;②64MB RAM;③1GB硬盘;④Pentium CPU。

软件主要特征:

①设计输入方式——原理图输入;②可观测电路的幅频和相频特性;③支持的器件:ispPAC10、ispPAC20、ispPAC80;④内含用于低通滤波器设计的宏;⑤能将设计直接下载。

(2)PAC-Designer软件的安装(略)。

(3)PAC-Designer软件的使用方法。

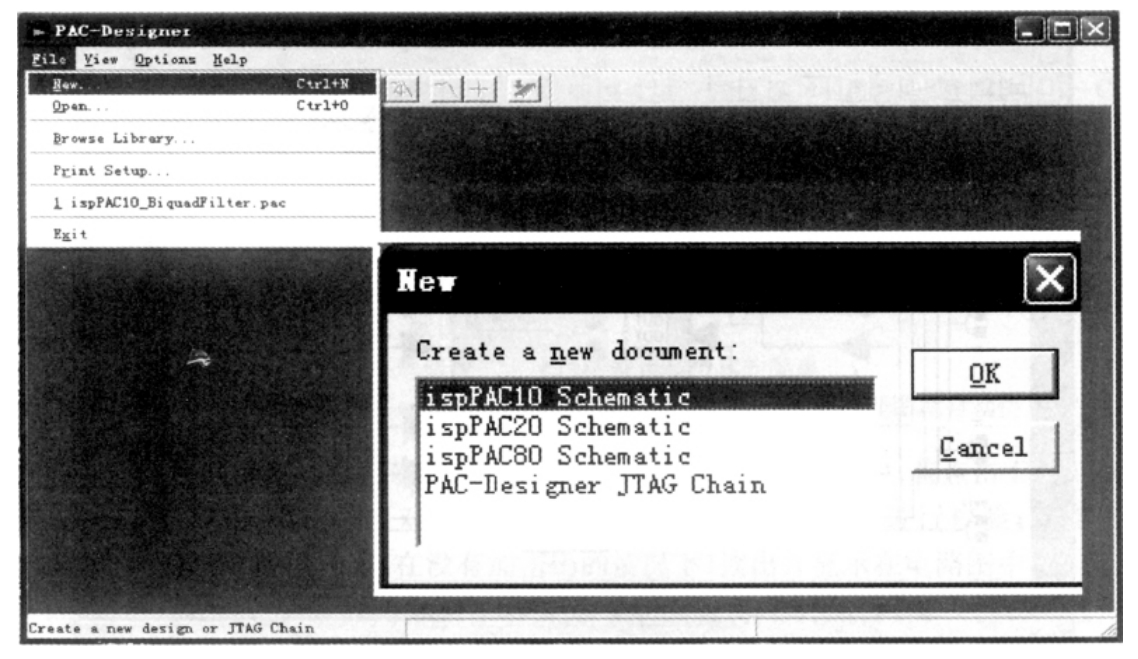

在Windows中,按“开始”→程序→Lattice Semiconductor→PAC-Designer菜单,进入PAC软件集成开发环境(主窗口),如图5.1.14所示。

图5.1.14 PAC-Designer主界面

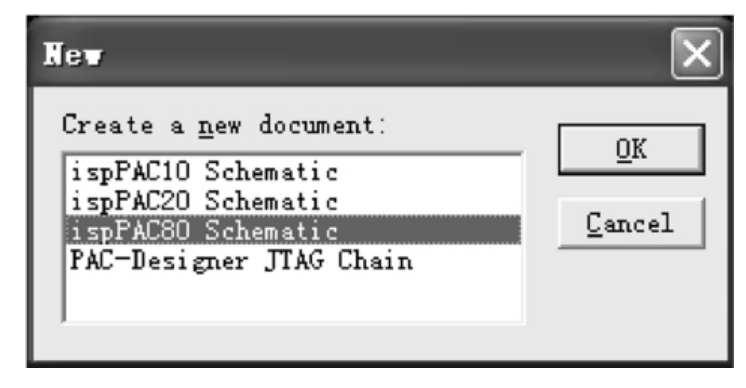

(1)为所要输入的电路图建立一个新文档

点击PAC-Designer主界面菜单条上的File,在其下拉菜单中选择New并单击它,就会弹出一个名为New的小窗口,如图5.1.14所示。在New窗口中选择一种与所采用的器件型号相对应的Schematic文档(本例选择ispPAC10),然后点击OK,就弹出一个电路图设计输入窗口,这是一张ispPAC10的内部电路图如图5.1.15所示。

图5.1.15 电路图设计输入界面

(2)编辑电路图连线

一开始所显示的电路图中各个PAC块均处于无任何连接的状态,现在根据所设计电路的要求,将电路中所需要的连线连接起来。方法如下:移动鼠标箭头到某个IA输入端,这时在输入端附近出现[ ]状态,双击[ ]一次,就会弹出一个名为Interconnect的小窗口,见图5.1.16所示。从该窗口列出的各引脚名中选择一个(图中选择IN1),点击OK确认后,在输入端与外引脚IN1之间就出现了一根连线,也可以用鼠标拖放的方式进行连接。重复上述过程直到完成整个电路图的连接。

图5.1.16 在电路图设计输入界面中编辑连线

(3)增益选择

将鼠标箭头移到某个IA的图符上,待出现[ ]状态符时,双击一次,就会弹出一个“Polarity &gain Level”小窗口,其中显示-10~+10所有整数值的增益,选择其中的一个并点击OK确认,该PAC的增益就设置好了。重复上述过程直到完成整个电路图的增益设置。仿照上述方法,还可以对输出放大器OA的反馈电容的值进行设置。顺便指出,这种设置方式不是唯一的,也可以在主菜单中选择Edit→Symbol→选择参数设置的对象。

当所设计的电路都完成了连线和参数设置后,按主菜单的File→Save。

(4)如果所设计的是一个低通或带通滤波器电路,当完成设计后,可以对设计作一次仿真,以验证电路的特性是否与设计的初衷相吻合。PAC-Designer软件的仿真结果是以幅频和相频曲线的形式给出的。仿真的操作步骤如下:

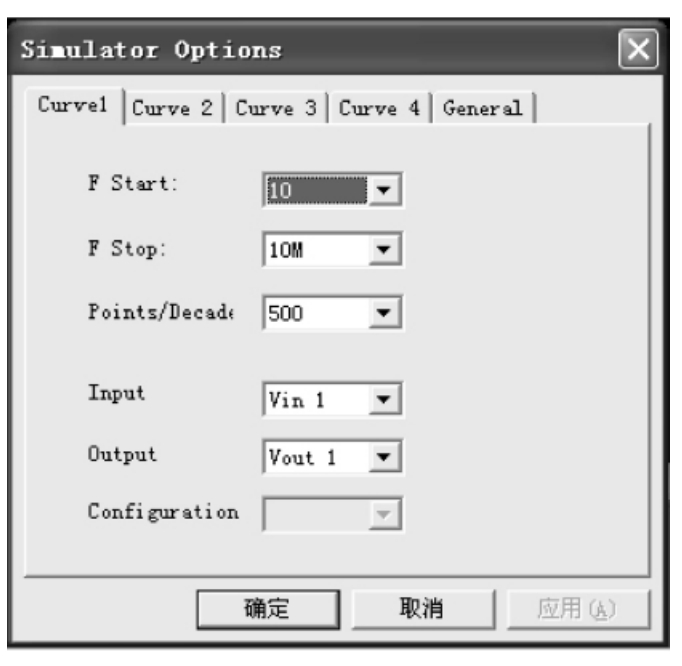

①设置仿真参数。按Options→Simulator产生如图5.1.17所示的对话框。

图5.1.17 仿真参数设置

对话框中各选项的含义如表5.1.4所示。

表5.1.4 图5.1.17对话框各选项的含义

②执行仿真操作。在完成仿真参数设置后,点击电路图编辑窗口的主菜单命令Tools→Run Simulator菜单进行仿真操作。

③器件编程。完成了设计输入和模拟验证以后,最后一步就是对器件进行下载编程了。首先要检查下载编程电缆是否将PC机(并行口)与下载板(26针插座)连接好了,下载板上的器件是否安装了,5V电源加了没有,一切准备就绪后可以下载了。

图5.1.18 选择ispPAC20器件

点击电路图编辑窗口的主菜单命令Tools,在Tools下拉菜单中,若点击Download,即可完成下载;若点击Verify,可对器件中下载的内容与原始电路图进行校验;若点击Upload,可将PAC芯片中的内容(在没有加密码的情况下)读出并显示在电路图中。

ispPAC器件设有一个加密保护区,如果所设计的电路需要加密,在下载后要选择器件内容是否允许被读出,起加密保护作用。具体操作如下:Edit→Security。

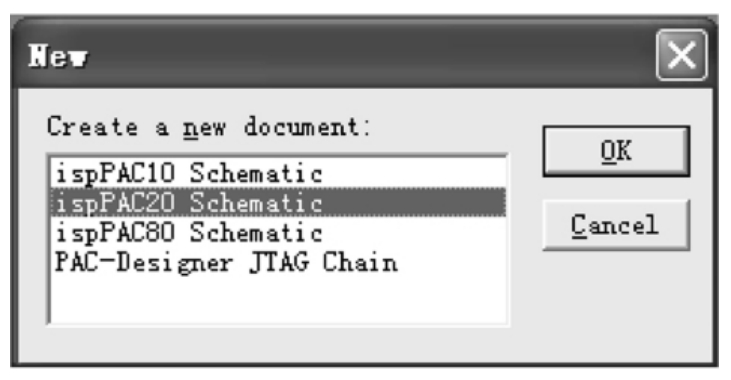

(5)ispPAC20器件的软件的设计方法

点击主界面菜单条上File→New,在如图5.1.18所示的New小窗口,点击ispPAC20 Schematic文档,如图5.1.18所示。点击OK,打开ispPAC20的编辑界面,如图5.1.19所示。

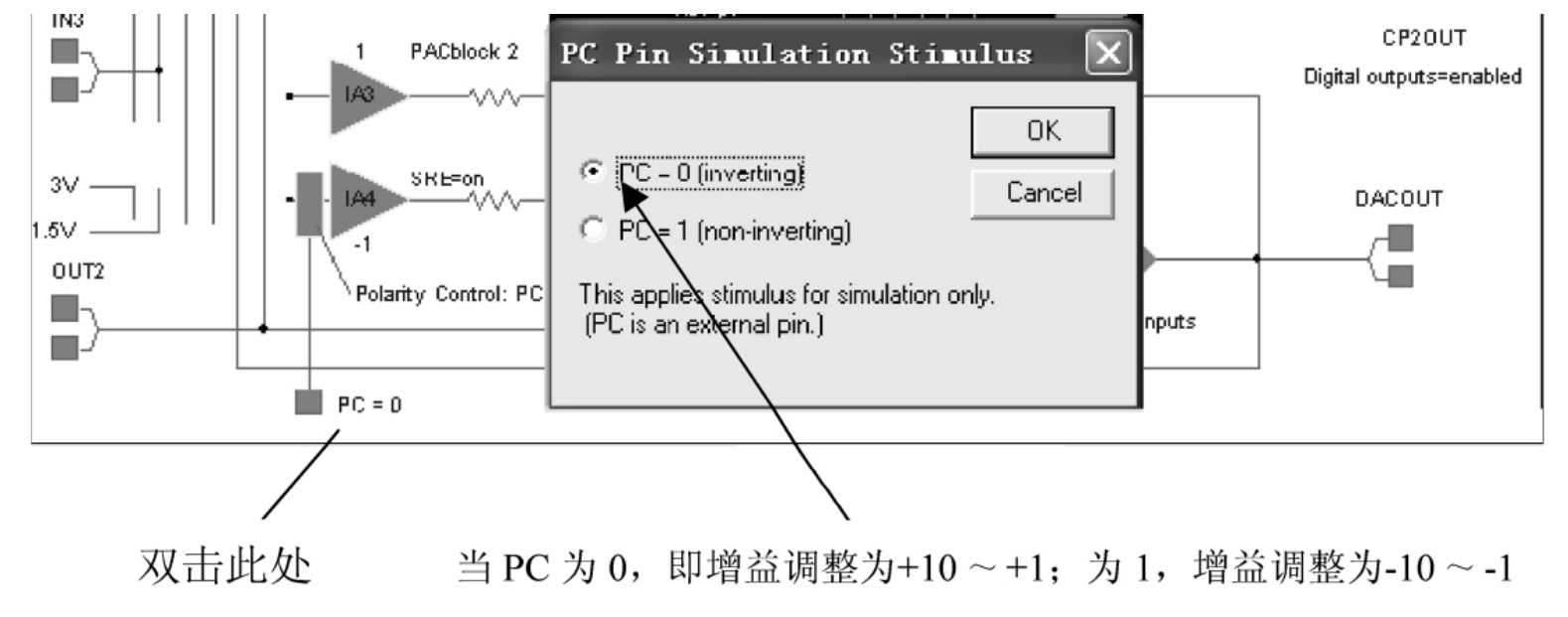

可以看到PAC20有两个基本单元电路PAC块。IA1模块增加了模拟2选1多路器,由引脚MSEL来控制,当MSEL为0时,a通道选通;为1时,b通道选通。IA4也增加一个极性增益控制端PC,可以通过外面的信号来控制,也可在内部软件控制极性进行模拟仿真,方法如下:双击PC=0/1处,可弹出一画面,如图5.1.20所示。

在PC=0/1之间进行选择,点击OK。

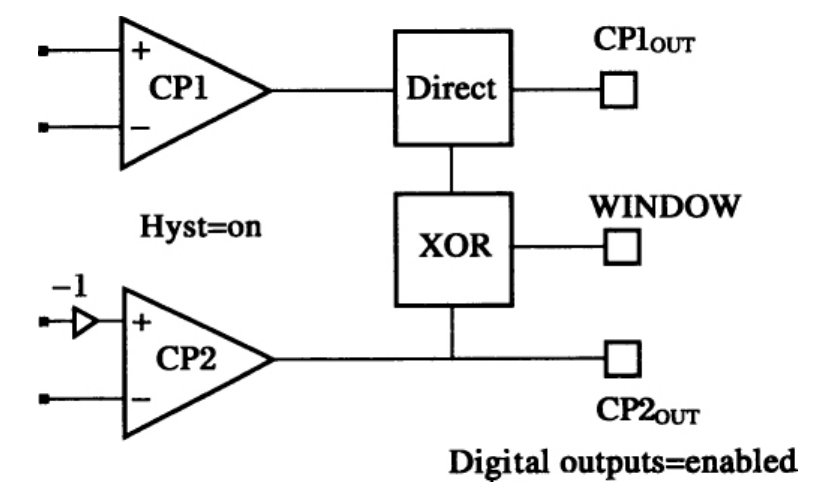

PAC20中有一对高速比较器CP1、CP2,如图5.1.21所示。它的输出方式有多种,可以直接输出,异或输出,还可以是以RS触发器的方式输出。

图5.1.19 ispPAC20电路图设计输入界面

图5.1.20 极性控制端PC的设置

图5.1.21 PAC20中的两个比较器

图5.1.22 CP1OUT的选择

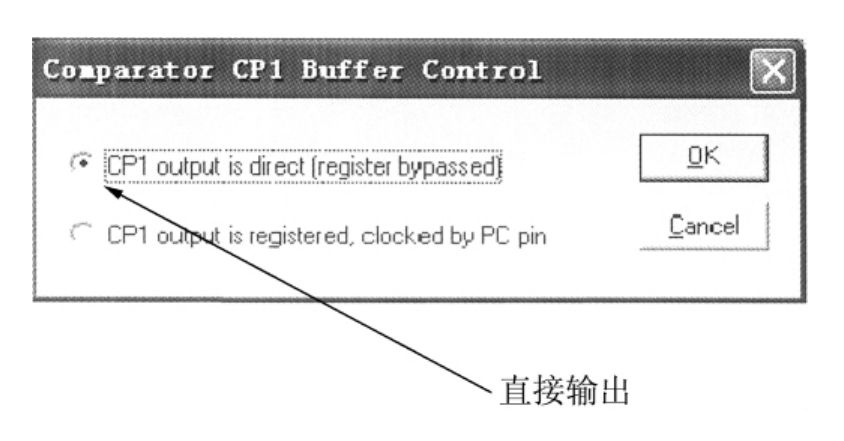

CP1OUT有两种输出选择,双击“Direct”处,可弹出选择窗口,如图5.1.22所示。

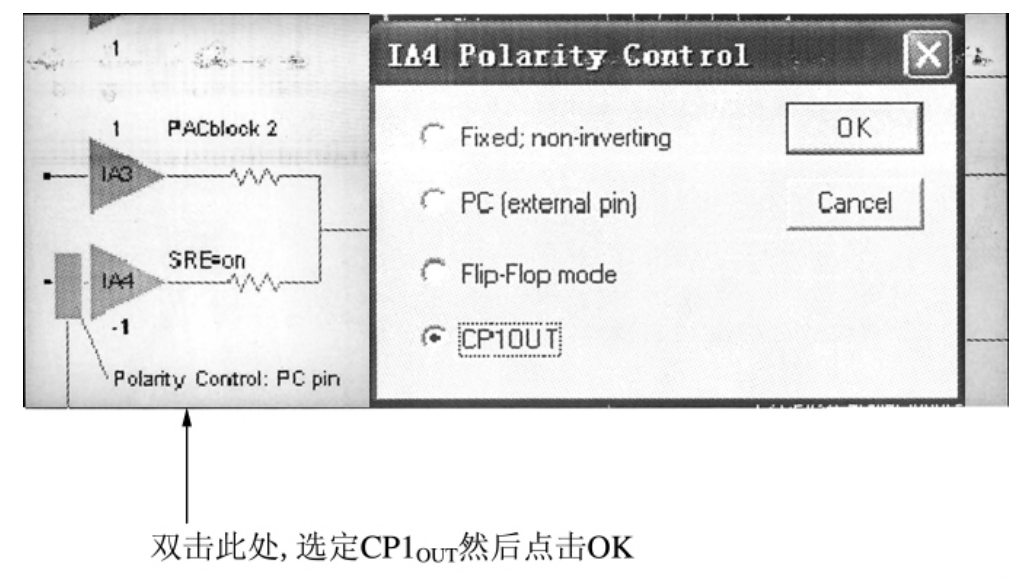

如果选定CP1output is registered,应在IA4中选定。方法如下:双击“Polarity Control:PC pin”弹出如图5.1.23中所示窗口,按图示操作即可。

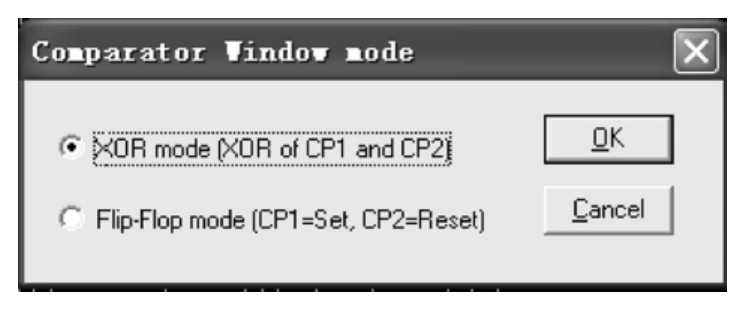

Window输出口有两种选择模式,双击“XOR”,可弹出图5.1.24所示窗口。选择XOR mode表示CP1与CP2是相异或的方式输出;选择Flip-Flop mode表示是以RS触发器的方式输出,功能由用户配制决定。

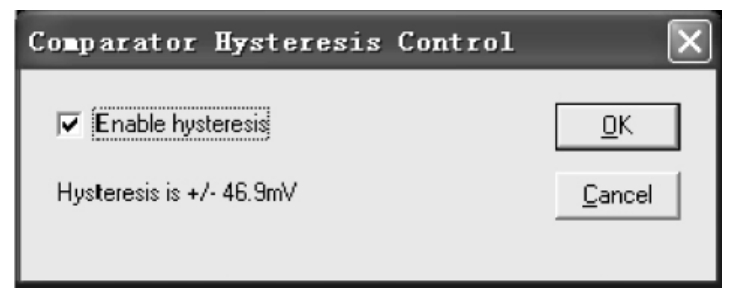

为了得到抗干扰能力比较强的比较器,在PAC20中设有一个迟滞控制的比较器,可以通过双击Hyst=on/off弹出图5.1.25的画面,通过使能的选择,点击OK。

回差电压为±47mV,它已经存放在E2CMOS存储器中,不可以设定。

图5.1.23 IA4极性控制

图5.1.24 比较器输出选择

图5.1.25 比较器的迟滞控制

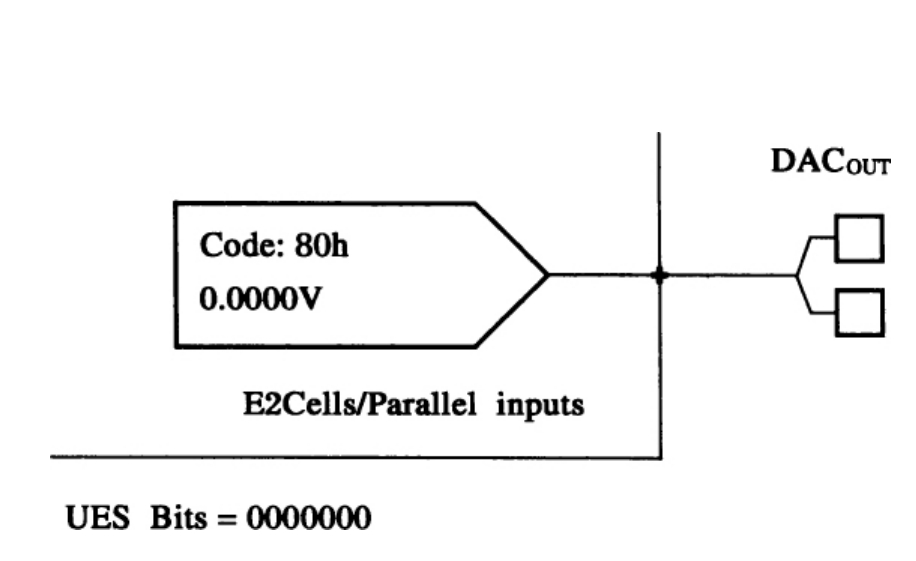

此外,PAC20有一个8位DAC模块,如图5.1.26所示。当D0~D7输入为00H~FFH时,转换电压为-3V~+3V的线性转换。

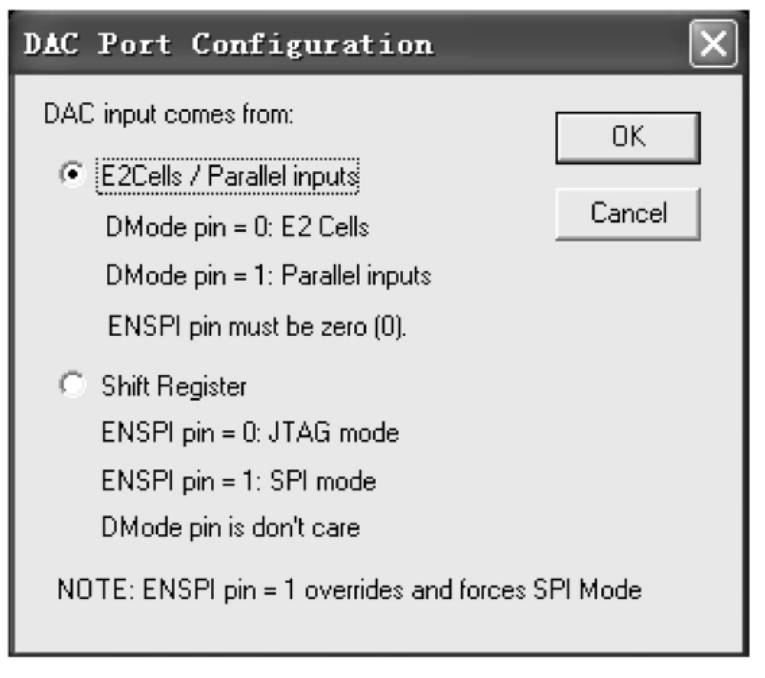

双击“E2Cell/Parallel inputs”弹出如图5.1.27所示的控制画面,选择适当的数据输入方式,点击OK。

具体D0~D7数据输入可以是外部输入数据,也可以是内部数据库,可以是串行输入,也可以是并行输入。如果选择E2Cell/Parallel inputs(此时的ENSPI管脚必须为0),当DMODE管脚为1时,外部输入数据;当DMODE管脚为0时,由内部数据库输入。如果选择Shift Register,此时DMODE管脚不起作用,ENSPI为1时,数据输入为JTAG模式,ENSPI为0时,数据输入为SPI模式。

图5.1.26 PAC20的DAC转换模块

图5.1.27 DAC输入方式的选择

(6)ispPAC80器件的软件设计方法

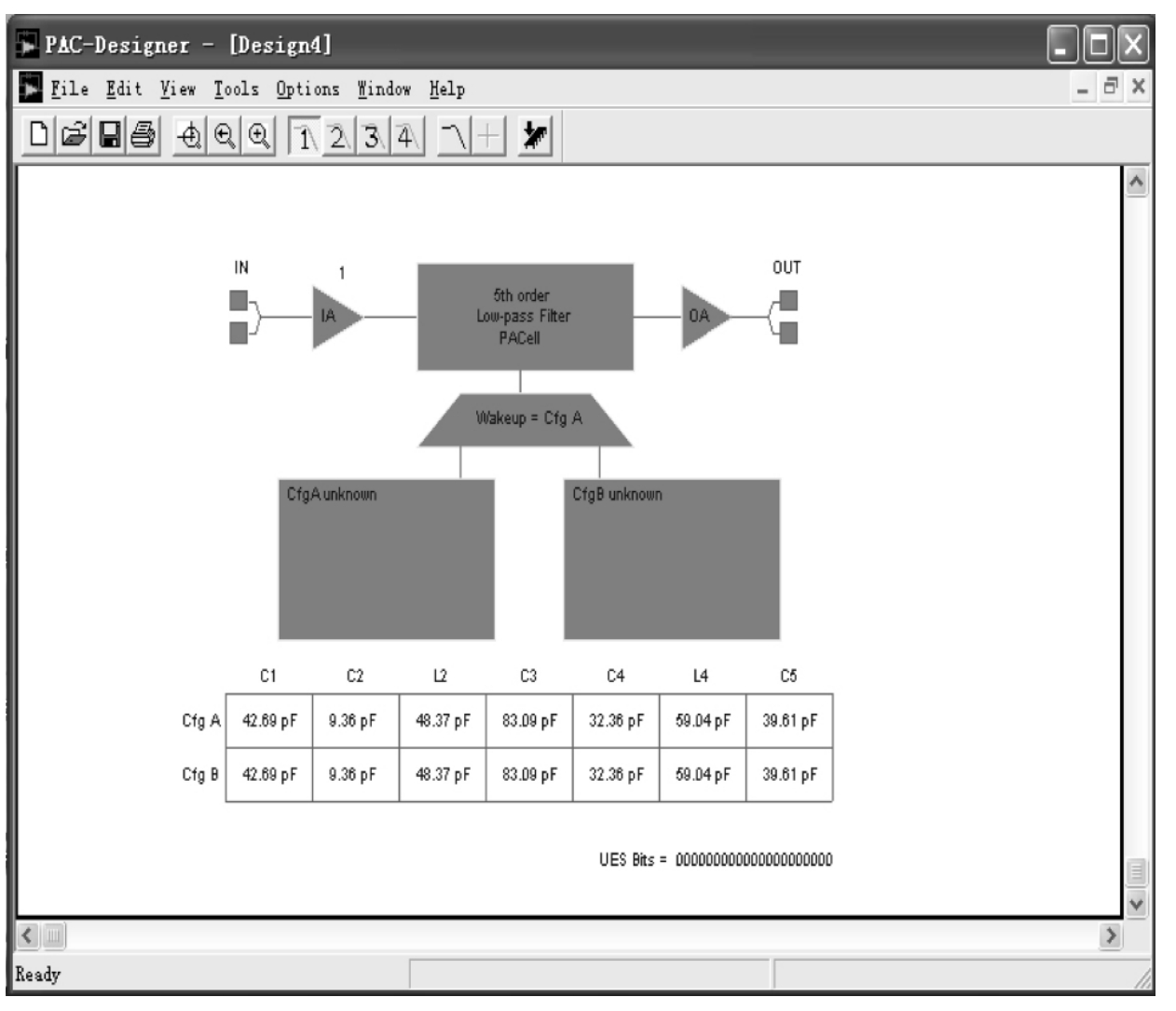

在设计输入处选择ispPAC80,如图5.1.28所示。点击OK,出现图5.1.29所示的isp-PAC80电路设计输入界面。

图5.1.28 选择ispPAC80器件

ispPAC80器件是一种专门用来实现高性能连续低通滤波器的可编程模拟器件。内含两个同时存储不同参数的五阶滤波器的配制(CfgA和CfgB),如图5.1.29所示。

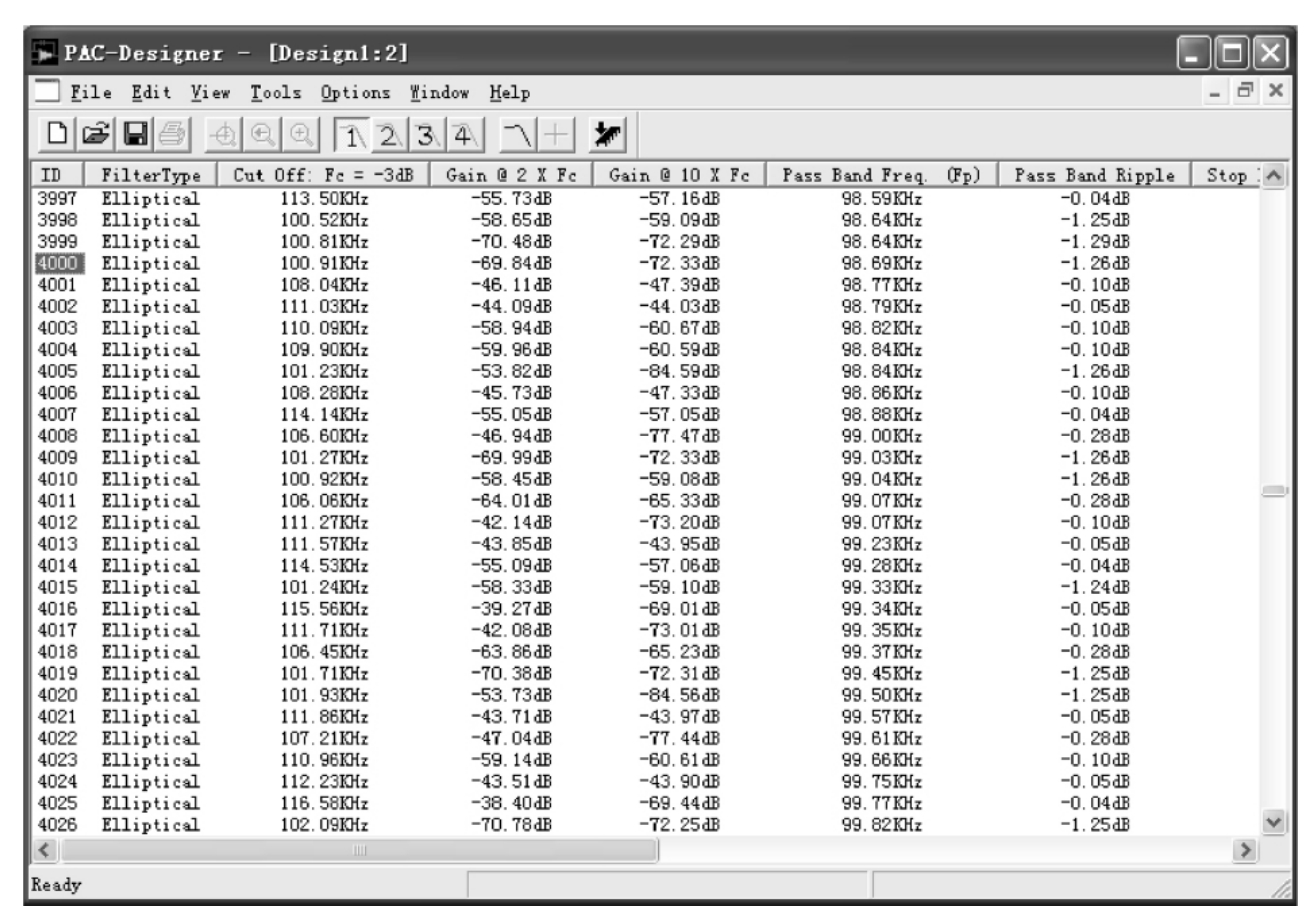

ispPAC Designer软件含有8 000多种不同类型和参数的五阶低通滤波器数据库,该库中含有各种不同类型的滤波器,如巴塞尔滤波器(Bessel)、线性滤波器、高斯滤波器(Gaussian)、巴特沃斯滤波器(Butterworth)、椭圆滤波器等,每种类型的滤波器根据其参数值的不同,又分为不同的具体型号,共计8 244种。设计者可以任意调用该库,极大地方便了低通滤波器的设计,用户只需具备关于低通滤波器的技术参数知识,根据所要设计的滤波器的目标数据,从数据库中挑选出与目标数据相接近的方案,将其Copy到CfgA或CfgB中即可。具体方法如下:先设计第一个配置(CfgA),双击CfgA unknown所在的矩形框,产生如图5.1.30所示的五阶低通滤波器库。

图5.1.29 ispPAC80电路设计输入界面

根据设计要求选定一种滤波器,如第4001种(ID号为4000)的椭圆滤波器,双击该ID号,将该种滤波器拷贝进ispPAC80的第一组配置Configuration A中。同样可再选一种滤波器并将其拷贝进Configuration B中。这时,图5.1.29中的ispPAC80图形设计输入环境变成图5.1.31所示。

图5.1.30 五阶低通滤波器库

图5.1.31 调入滤波器库后的ispPAC80图形设计输入环境

在图中,双击输入仪表运放IA图标,可以调整输入增益倍数(1,2,5或10)。同样,双击Wakeup=Cfg A的梯形图标,可以设置激活配置Cfg A或Cfg B。

在上述设计输入完毕后,接下来可以进行仿真,按Tools→Run Simulator菜单执行。如果模拟出来的幅频、相频特性满足要求,就可以对ispPAC80器件下载编程,一个高性能的低通滤波器就被制作成功。

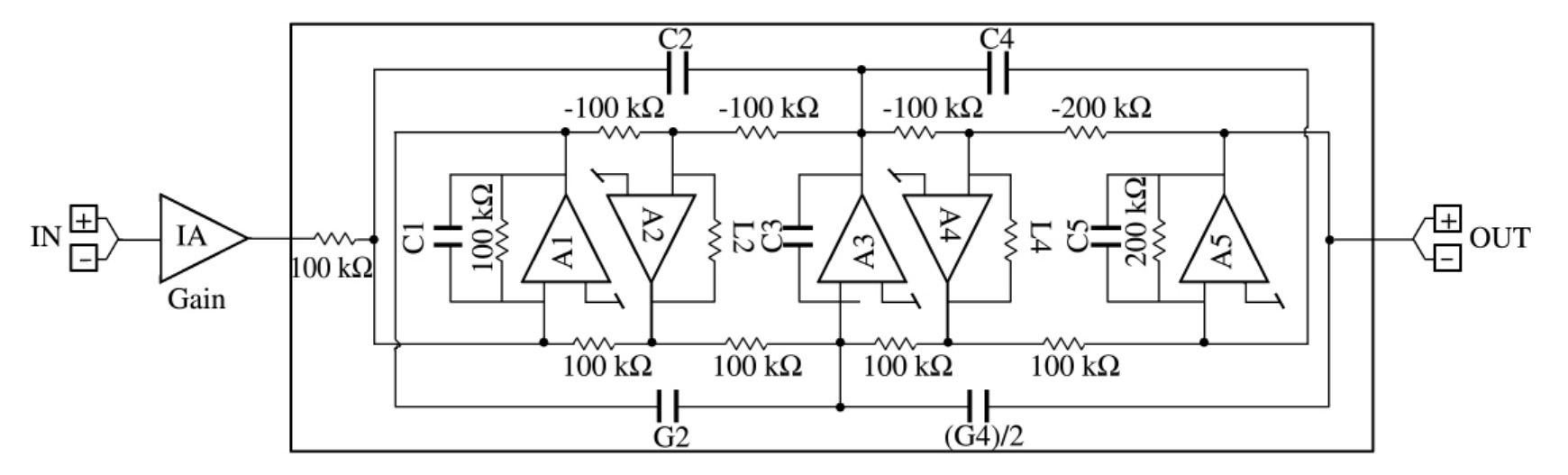

若仿真结果仍与设计要求有所偏差,则还可以调整图中的滤波器参数C1、C2、L2、C3、C4、L4和C5(双击该处即可进入参数调整状态)。这些参数的含义如图5.1.32所示。

图5.1.32 ispPAC80内部的五阶滤波器简化结构示意图

上一篇:预算约束条件

下一篇:石羊河流域水资源利用中心简介