10.4 高速高增益运放系统设计

在数模混合电路设计中,需要充分利用现有的深亚微米CMOS工艺实现低压、高速、高精度的模拟集成运算放大器。通常,速度和精度的要求相互矛盾并相互制约,精度要求采用大的器件尺寸(L)、低的静态电流和多级结构,而速度则要求小的器件尺寸(L)、大的静态电流和单级结构。为适应低压高电源抑制比的需要,全差分运算放大器广泛应用于现代高速、高精度模拟信号处理系统之中。

10.4.1 高速运放的系统结构

1)Cascode运放

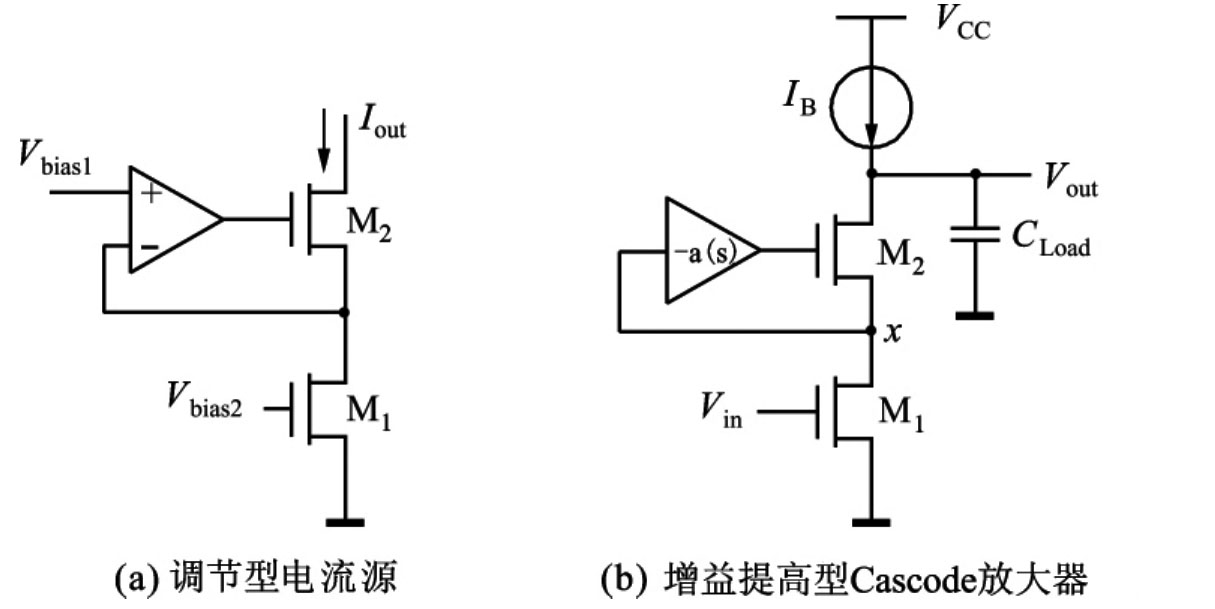

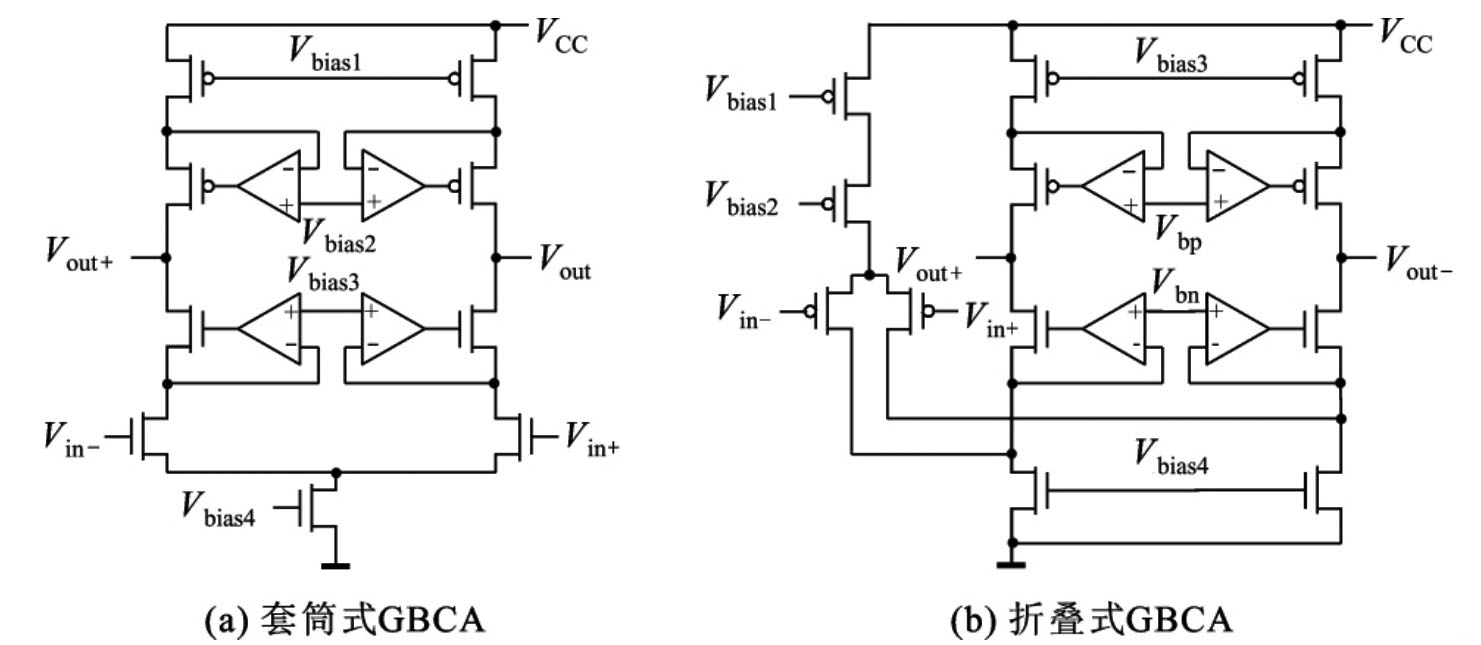

Cascode是实现高速运放系统的首选结构。从小信号分析的角度出发,Cascode可以很好兼顾带宽与增益的要求,以单级低频极点的优势实现两级甚至多级增益的电压放大功能。进一步提高增益还可采用多级或多层Cascode结构,如图10-1所示。

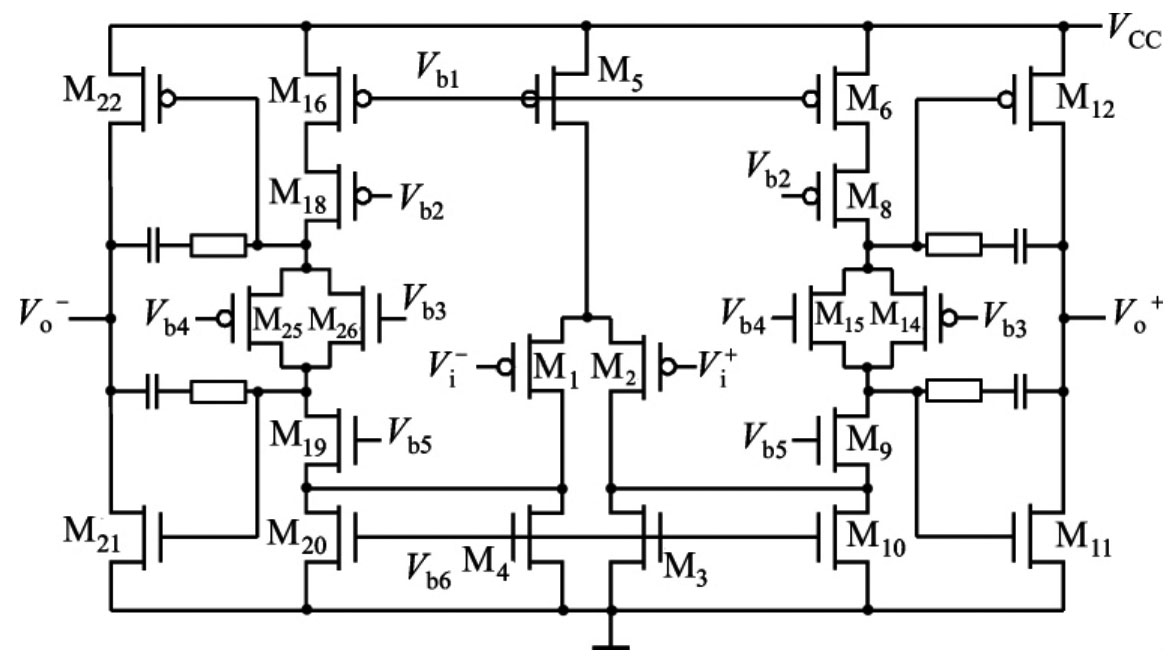

图10-1 两级Folded Cascode全差分Class AB输出结构

图10-1所示的两级全差分结构中,输入级为PMOS差分输入的折叠式Cascode结构,输出级采用Class AB的互补推挽放大驱动,其中Vb3/Vb4偏置的M14/M15和M25/M26提供差分输出级的Class AB偏置,Vb6偏置由CMFB的输出提供,通过第一级差分输出,控制第一级输出结点的静态工作点电位,同时在输出级采用串联调节电阻的Miller电容补偿,由此构成稳定工作的两级全差分放大器。

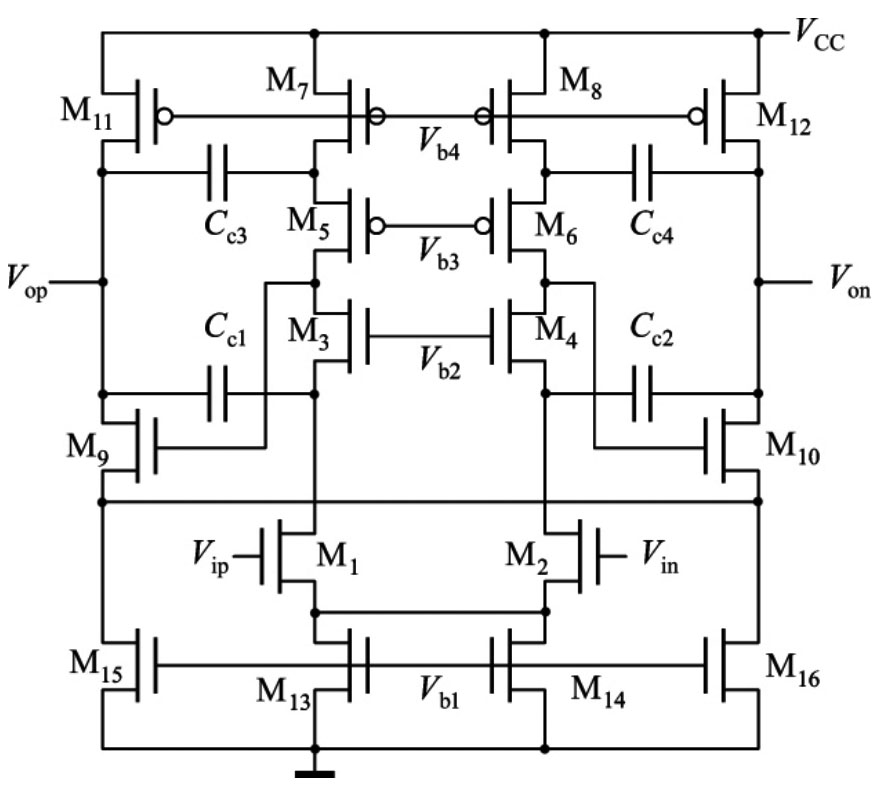

图10-2为另一种类型的两级Cascode增益结构。输入级采用NMOS差分对的套筒式Cascode放大,第二级仍为NMOS差分输入的CS全差分增益级。与前一种两级全差分电路相比较,本电路两级全差分结构的每一级全差分输出共模信号均无定义,因此,应对第一级全差分输出采用CMFB控制其合适的静态工作点,并调节此静态工作点使第二级的全差分输出位于合理的工作点。Vb1由附加的CMFB电路控制,分别稳定两级全差分输出的前后两级静态工作点。对于某一输出支路,采用两路并联的Cascode Miller电容补偿。以Von输出支路为例,CC2经过与M4管的CG Cascode电阻串联形成一路补偿,CC4与M6管的CG Cascode电阻串联形成另一路补偿,且两补偿支路之间为并联关系,最终形成稳定的两级全差分放大电路。

以上两类全差分Cascode电路具备三级单级电压增益能力,形成的3个极点中,第一级Cascode增益级的输出为低频主极点,输出级产生一个次极点,另外CG结构还形成一个高频次极点。两级结构中的输出级极点由于频率不高,对电路带宽扩展存在一定的抑制作用。为此,在牺牲低电源电压工作性能的前提下,可通过采用多层Cascode结构弥补以上不足,这样可消除原来的一个中频次极点,系统在保留原有主极点基础上,仅引入两个以下的高频次极点。

图10-2 两级套筒式Cascode全差分放大电路

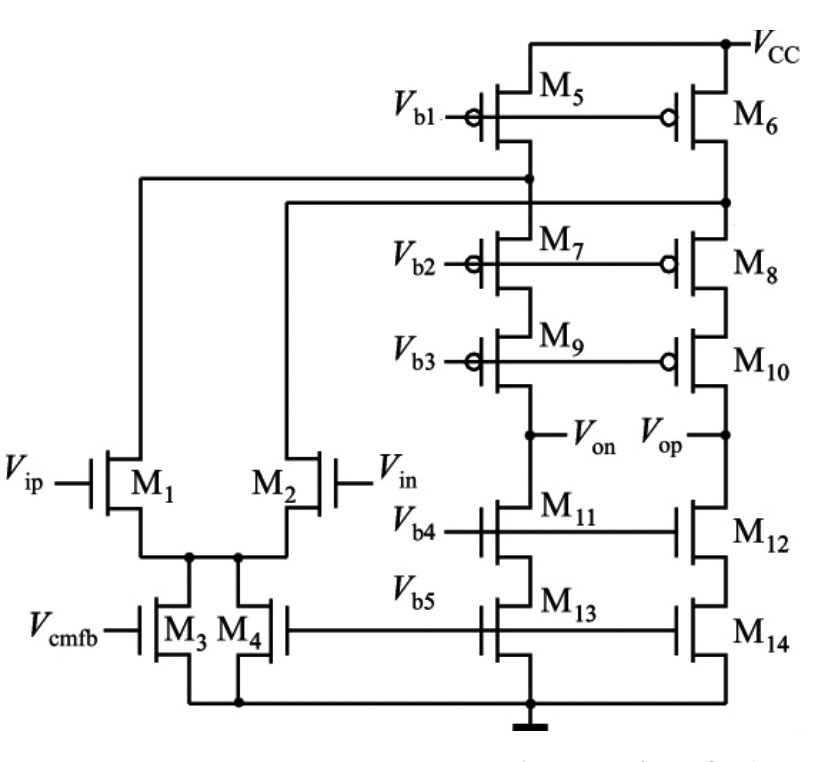

图10-3 三层折叠式Cascode全差分放大电路

图10-3给出了一种准三层折叠式Cascode单级放大电路,该结构折中考虑了高增益和低电源电压的要求。其中输出级仅在VCC方向上增加了一层Cascode管,电源电压的提高幅度有限,而输出到GND之间仍然保持原有的基本Cascode结构,这样输出阻抗仅由直流对地的Cascode管的输出阻抗决定,增益比普通Cascode结构增加了近1倍。

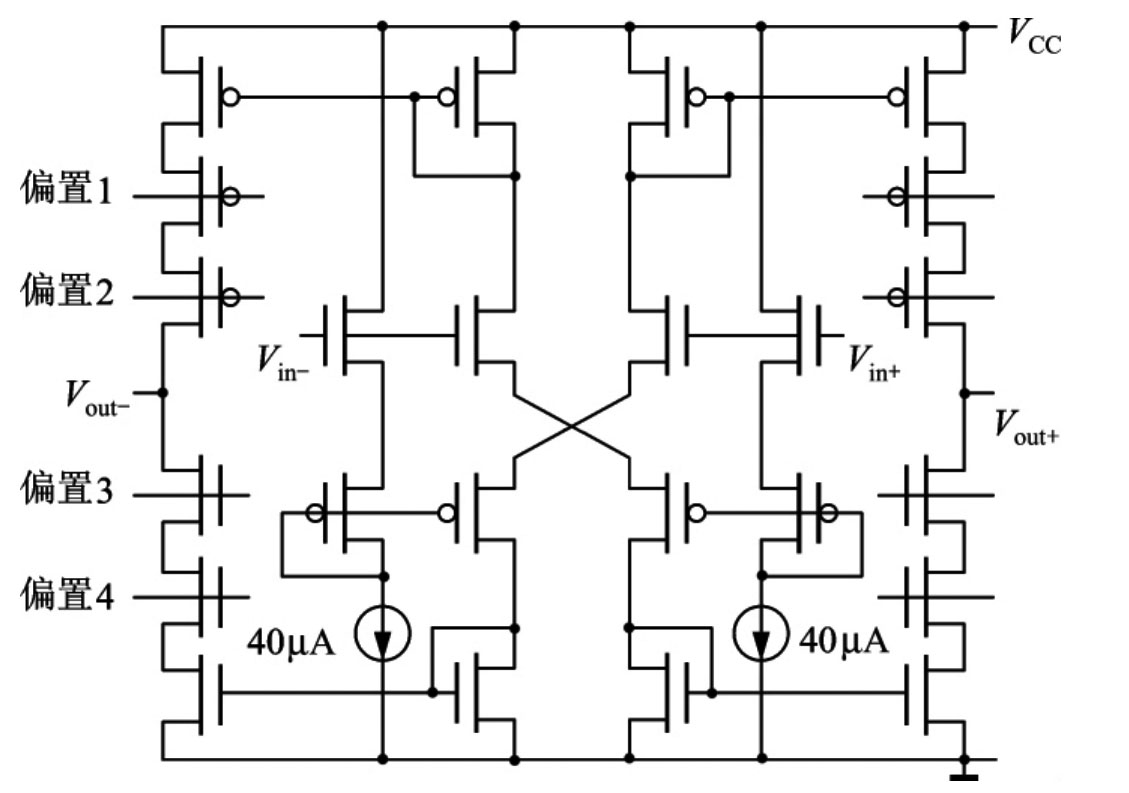

图10-4 多层Cascode Class AB的单级增益结构

以上各类Cascode放大电路的输入级还可采用Class AB的差分输入结构如图10-4所示。在速度特性方面,通过消除普通差分对恒定尾电流的限制,通过动态增加大信号时的尾电流值,提高大信号下的瞬态响应速度,从而提高电路整体的速度性能。在增益方面,输出级可采用多层Cascode以提高输出阻抗,满足精度要求。此外,Class AB还可通过输入差分对非线性项的相互抵消,实现线性范围与动态范围的近似相等,降低非线性失真。

多层Cascode的主要不足是所需的电源电压较高,在低压高速运放的设计中应用难度较大。为避免这个缺点同时保留其高增益的特色,可采用增益提高的Cascode放大电路。这种电路具有单级增益的带宽性能和多级增益的放大性能,由此在高速、高精度信号处理领域得到了广泛的关注和实际的应用。

2)增益提高型Cascode结构

增益提高型Cascode放大器GBCA(Gain Boost Cascode Amplifier),可以实现增益、带宽和低压工作的有效兼顾。在深亚微米条件下,普通的Cascode Amplifier直流增益仅能达到50~60dB,对高精度所需要的至少80dB的要求尚有一段距离,而增益倍增技术可以在已有基础上进一步提高增益,且带宽、速度和最低电源电压等方面可避免过大的负面影响。

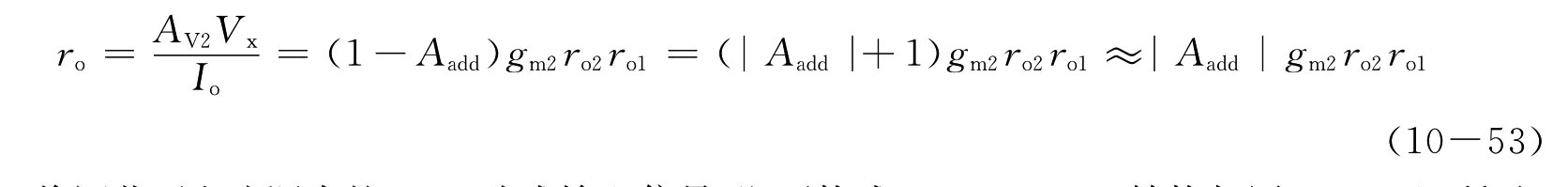

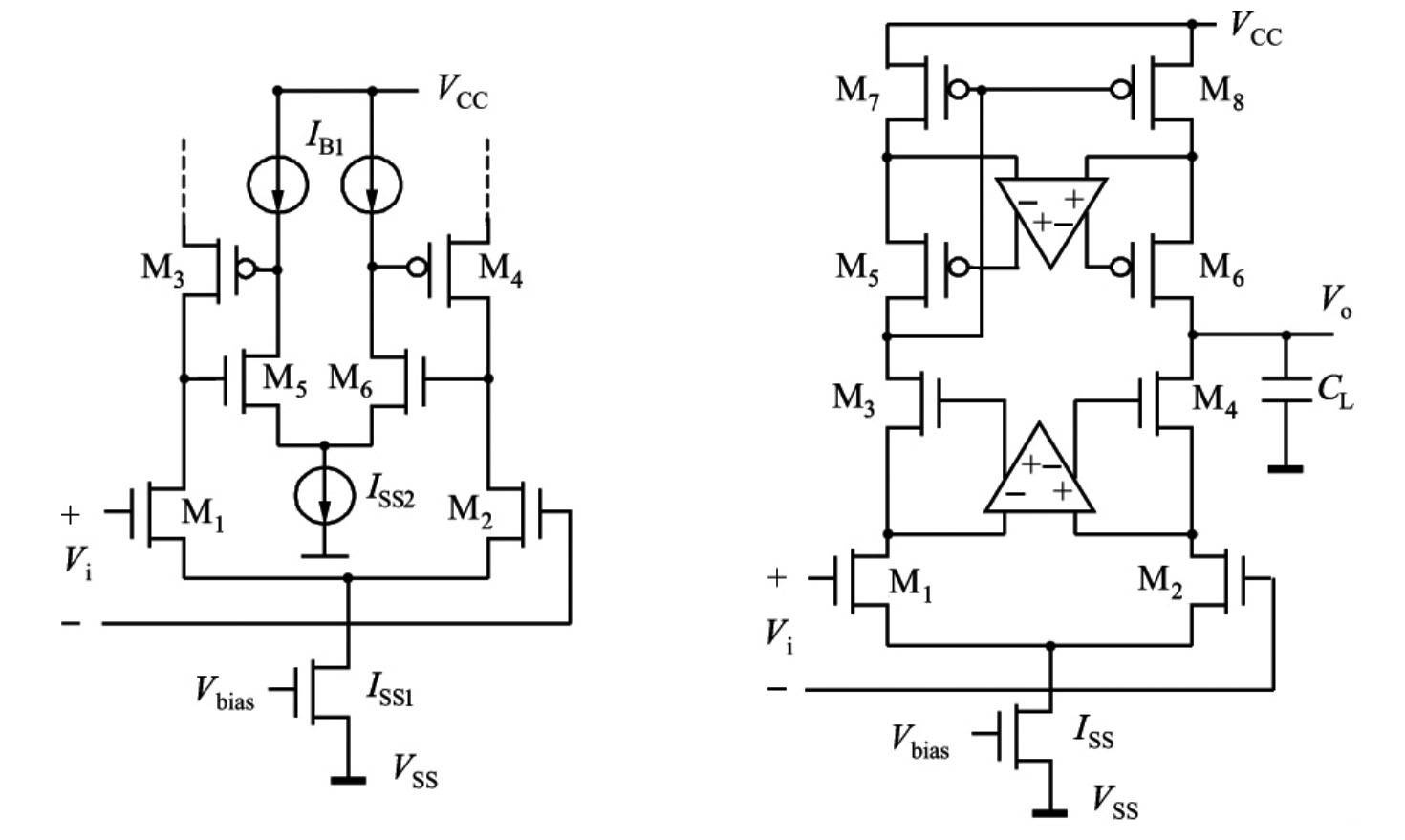

Gain Boosted实现的基本原理是基于图10-5(a)所示的调节型电流源电路结构,即通过提高输出结点的阻抗而实现增益的提高,避免多级增益中低频次极点的引入。当不存在辅助运放而采用Vbias1直接偏置时,则还原到普通Cascode电路。根据电路结构,常规Cascode的输出阻抗为ro=AV2Vx/Io=gm2ro2ro1。

图10-5 增益提高的Cascode放大器

由于M2管构成环路的电压同相跟随器,为保证环路的负反馈性质,辅助放大器必须为反相放大器,当采用差分辅助运放时,反馈电压Vx必须接辅助差分运放的反相位输入端。在此条件下,M2管的源电压变化信号Vx经过Aadd<0的反向放大,加入到M2管栅上的信号近似为AaddVx,则M2CG管的有效激励电压为Vx-AaddVx=(1-Aadd)Vx。因此,当采用调节型增益倍增技术后,直流支路输出到GND的阻抗变化为

将调节型电流源中的VBIAS2改成输入信号,即可构成Gain Boosted结构如图10-5(b)所示。为保持增益的改善,直流支路输出到VCC的阻抗变换应与以上到GND支路的输出阻抗相匹配,在此条件下并联阻抗近似为单支路阻抗的一半。取m≈0.5,则其直流增益为

在负载CL下主运放的单位增益带宽为

式中,Aadd为辅助运放的反相电压增益,在其极点频率远大于主运放的GBW条件下,主运放单级增益的高速性质得以保存。

因此,Aadd通常采用宽带单级增益结构,以最大限度降低对主运放速度性能的影响。从增益的角度看,GBCA可以等效为Aadd的增益级与CS-CG Cascode增益级的级连,所以优化设计辅助运放的增益和频率特性十分关键。

若辅助运放采用差分运放结构,则辅助差分输入信号的共模信号的范围受到Aadd输出摆幅下限和Vx下限的限制,Vx下限为主NMOS放大管的Δn饱和压降,否则当Aadd参考电压提高后,主放大器输出电压的最低值由2Δn增加到Δn+Vref1。同样,对于与之对称的P型GBCA,辅助运放差分电压的输入参考值受输出摆幅上限的限制,主放大器输出电压的最高值由VDD-2Δp减小到Vref2-Δp。输出电压摆幅为Vref2-Vref1-Δn-Δp,摆幅降低为VCCVref2+Vref1-(Δn+Δp)。

以上分析表明,Cascode放大器是一种能将精度与速度特性很好结合在一起的电路结构,即采用单级高速增益结构实现多级高增益的功能。进一步增加增益需要采用多层Cascode以提高输出阻抗,但多层Cascode受到较高工作电压的限制,或者说在低电压工作下的输出摆幅很小。此外增益要求大的L与小的电流I,与高速所要求的小L、大电流I相互矛盾,难以兼顾。因此,保持单级增益性质的GBCA和折叠式多层Cascode Class AB则逐步成为高速、高精度模拟信号处理系统中的主流结构。在保持原有结构特点的基础上,低压高稳定设计成为其中的难点。

10.4.2 高速GBCA运放结构设计

GBCA设计关注的重点在于提高输出信号摆幅范围、降低最小工作电压、提高对共模噪声的抑制。因此,全差分GBCA成为高速、高精度模拟信号处理领域中的主流运放结构。

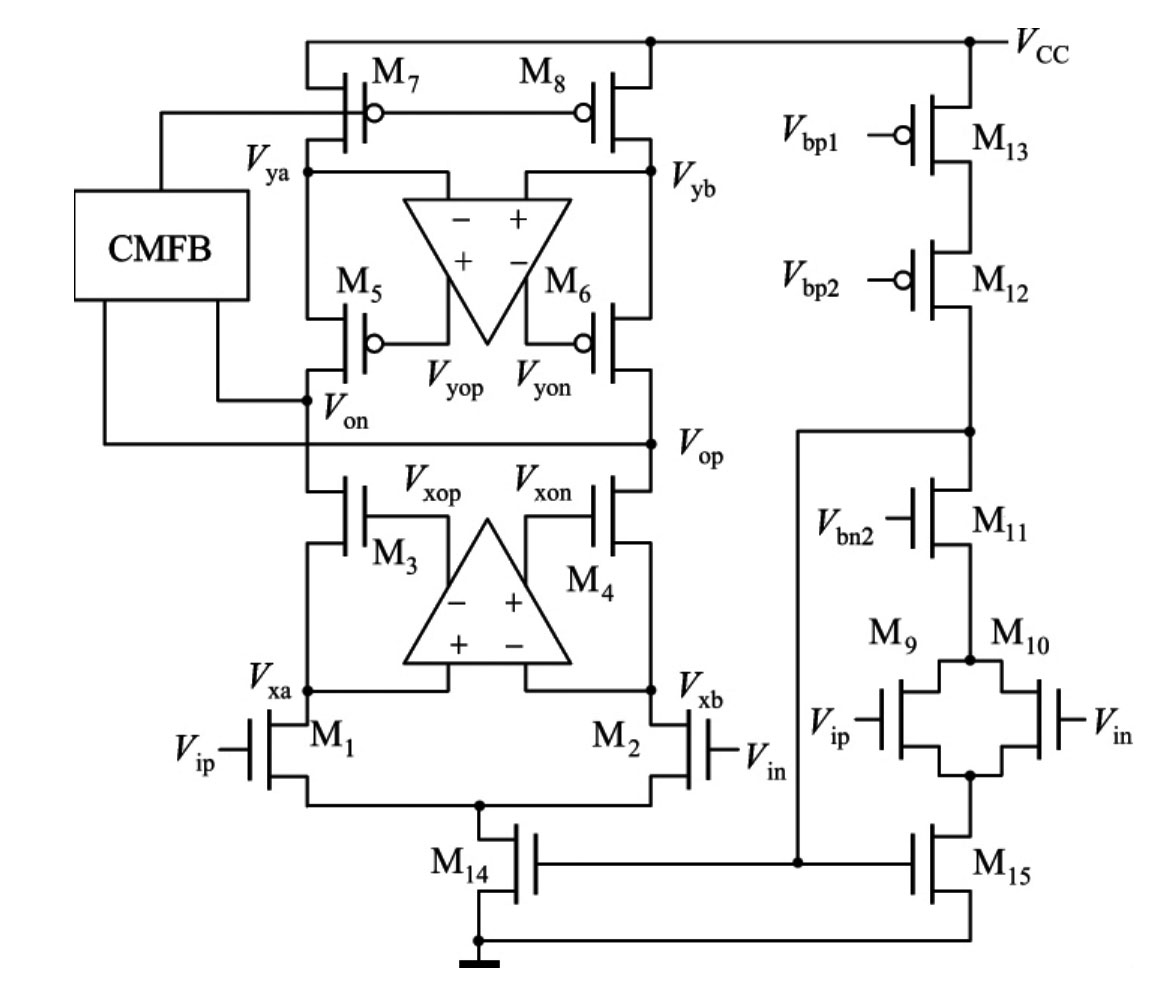

1)直流特性分析

图10-6给出了GBCA电路的几种具体实现方式,主要区别在于所采用的辅助运放不同,造成输出动态范围的差异。考察M2CG管x结点信号电压,在第一种常规结构中,由于负反馈CS M3管的VGS钳位作用,使得Vx的最低值比理想的过驱动电压近似增加一个VTN开启电压,因此该结构不太适合低压应用,但辅助运放只额外增加一个低频极点,对系统稳定性的影响最小。此外,由于M2寄生Miller电容引入的偶对,对系统的瞬态响应特性有一定影响。

图10-6 GBCA增益单元电路中的辅助运放结构

第二种电平移位结构可以克服前一种的不足,Vx电位向上平移动VGSn≈VTN+Δn后再驱动辅助运放的输入,因此Vx可以降低到电路允许的最小值,即M1管的一个过驱动电压的大小,因此该结构适合低压工作,代价是增加了低功耗支路电流的消耗,同时增加了一个由电平移位管所引起的高频极点,对系统稳定性和瞬态响应特性产生重要影响。

第三种是辅助运放采用折叠式Cascode结构,辅助运放PMOS输入管的输入信号对Vx的下限没有限制,Vx同样可以降低到最小值约为一个过驱动电压的大小。但该结构中的辅助运放同样引入一高频极点,对稳定性和瞬态特性的影响同样存在。

以上三种结构的主放大器都是单级CS结构,输入信号的共模范围受到严格的限制,大致在一个VGS附近。因此,为扩展输入信号的共模范围,主运放也应采用差分放大结构,由此构成全差分GBCA结构。显然,全差分GBCA一共需要4个如图10-6所示的单元结构,其中两个用于差分输入,两个用于负载。每个辅助放大器又有普通放大、差分放大两种选择。因此全差分GBCA存在多种结构上的变化,主要体现在辅助运放上,可以采用4个独立的单级放大单元,也可采用4个独立的差分放大,或两个独立的全差分放大器。

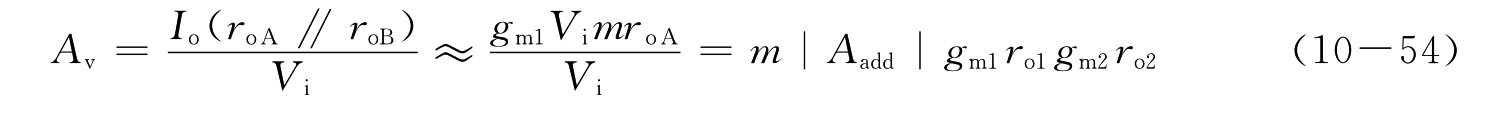

图10-7 四辅助单级放大的GBCA结构

图10-7给出了采用4个独立辅助放大器的GBCA电路结构,其中辅助运放采用了具有电平移位功能CS-CG的单级Cascode结构,而主运放则采用套筒式Cascode结构。为克服主运放输出摆幅小的缺点,并增加摆幅,采用了一种不同于常规的尾电流偏置技术,其关键在于保持恒流特性的条件下减小尾电流M14/M19上的压降。如果该尾电流源的漏源两端的电压降低ΔV,则输出摆幅可以提高ΔV。为此引入尾电流复制反馈技术,可以将M14/M19偏置在线性区,同时保持尾电流恒定不变。恒流复制结构由M14、M19、M38、M41管组成。其工作过程为:当M14/M19的漏端电压随输入共模电压而改变时,M38的漏端电压就会发生相应的变化,由于M42/M43中提供的恒定电流也流过M38,这样M38的栅极电压会自动调整,从而保证M14/M19中电流不变。采用共模反馈CMFB电路控制全差分运放输出的共模电平,通过共模负反馈作用调节PMOS恒流源的大小,改变与NMOS饱和电流的交点位置,实现对全差分输出静态工作点的精确控制。

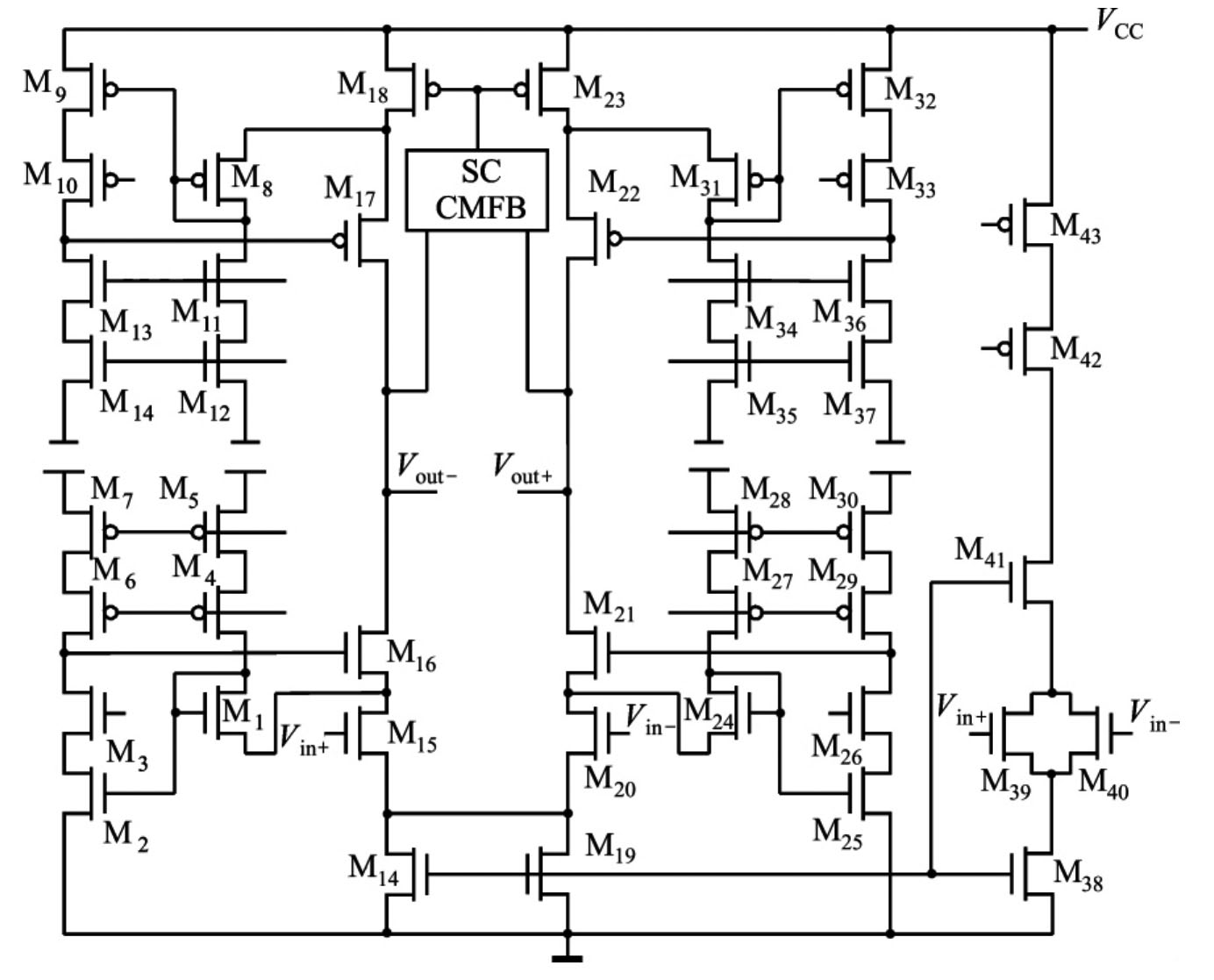

图10-8给出了采用差分辅助运放的GBCA电路结构,驱动NMOS管的辅助运放由于输入共模电平较低,辅助运放需采用PMOS差分输入级,同样驱动PMOS管的辅助运放需采用NMOS差分输入级。图10-8(a)中的主运放采用的是套筒式结构,根据已有的分析结果对输入信号共模电平的上限范围存在限制,因此对驱动NMOS管的辅助运放输入偏置电压提出具体要求,应满足Vbias3>Vi_CM-VTN的条件,导致该类型GBCA电路的应用受到一定限制。图10-8(b)中的主运放采用的是折叠式Cascode结构,该结构消除了对输入共模信号范围的限制要求,扩展了此类型GBCA电路的应用领域。一种采用4个折叠式Cascode辅助运放的全差分折叠式Cascode电路如图10-9所示。

图10-8 四个辅助运放套筒式和折叠式GBCA增益结构

图10-9 全差分GBCA电路

进一步分析发现,图10-8中的两个同类型的辅助差分放大器可以两两合并,分别组成1个独立的N型和P型输入的全差分辅助运放电路,并组成如图10-10所示的反馈控制结构。图10-11给出了主运放为套筒式Cascode、而辅助运放采用两个全差分增益的GBCA电路结构。需要特别指出的是,当套筒式主运放采用全差分辅助运放控制后,原套筒式GBCA中辅助运放固定偏置对输入信号共模电平范围限制的问题得到解决,其原因在于全差分结构的输入和输出电位可以在一定的范围内通过内部CMFB自主调节,无需外部提供固定的输入偏置。

图10-10 两个辅助差分运放套筒式单端输出GBCA增益结构

图10-11 辅助全差分运放调节的套筒式全差分GBCA增益结构

比较以上各种变化的GBCA电路,辅助运放采用全差分结构可缓解对输入共模信号范围的限制,实现最大的输出摆幅,这一点相对普通辅助放大器体现出优越性。在采用差分输入的辅助运放中,差分输出结构的复杂性与普通非差分结构相比大体相当,因为在全差分结构中需要增加CMFB结构。辅助运放可以采用图10-1~图10-4所示的Cascode增益结构,可以是单级或两级放大。更为有趣的是,两个全差分辅助运放自身也可采用折叠式GBCA结构,形成GBCA的嵌套式应用。

综上所述,全差分套筒式Cascode与全差分折叠式Cascode是GBCA主运放电路采用的主流结构,辅助运放多采用普通Cascode或全差分Cascode增益结构,甚至是GBCA的嵌套结构,导致其电路系统设计复杂,包括静态工作点的设定和动态范围的控制,最小工作电压与电路体系结构的关系,系统零极点分布对频率和稳定性影响等。此外,在GBCA运放系统结构基本确定的前提下,系统精度和速度性能的进一步提高,还紧密依赖于器件参数的优化设计。

10.4.3 高速GBCA频率特性设计

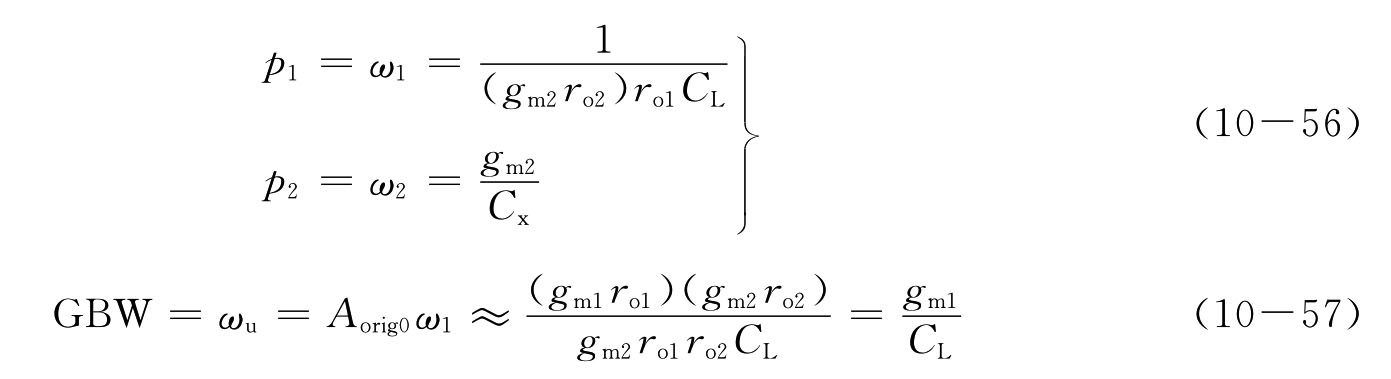

前文重点给出了GBCA电路结构体系的设计和直流特性的分析,该电路设计的难点之一在于频率特性的控制。需要指出的是,GBCA的频率特性与两级增益结构有本质区别,起增益倍增作用的辅助(反馈)放大器在其中起到十分关键性的作用。在忽略高频次极点作用的条件下,理想GBCA放大电路应保持普通Cascode放大器单级增益的频率响应特性,如图10-12所示。图中,Aadd为辅助运放增益的幅频特性,Aorig为不加辅助运放的主运放Cascode电路的幅频特性,Atot为GBCA运放系统总增益的幅频特性。

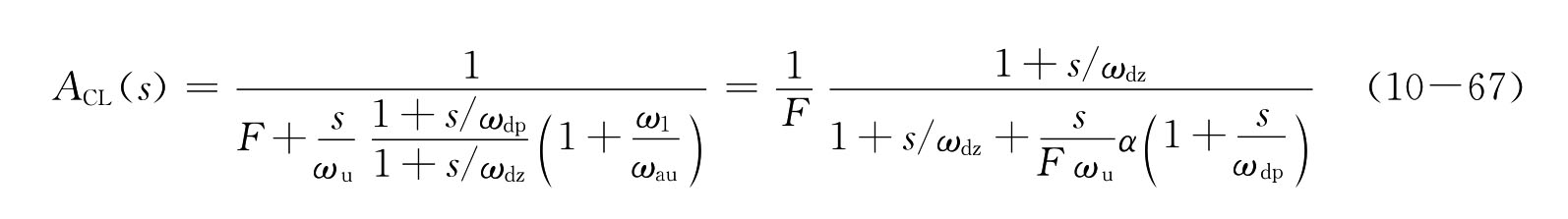

主运放Aorig为CS-CG的Cascode开环放大增益结构,这是一个典型的两极点增益系统,设ω1,ω2,ωu分别为CS-CG Cascode主运放的主次极点频率和单位增益带宽,即

图10-12 CA、GBCA的频率特性

由于Cx《CL,次极点ω2》GBW,主运放的稳定性容易得到满足,即主放大器保持单级增益放大器的频率特性,同时低频增益具有两级电压增益的性质。当采用辅助运放后,系统电压增益提高的方式与Cascode增益提高的方式相类似,即辅助运放对主极点的压缩仅通过输出阻抗的变换方式实现。由于输出阻抗与频率无关,因此主极点压缩与辅助运放的直流增益有关,当其带宽大于Cascode主运放带宽时,如图10-12所示,辅助运放极点影响可以忽略。Cascode增益提高方式是通过增加输出阻抗以实现增益的倍增,同时实现主极点的压缩;而级联(Cascade)则是通过增益的乘积实现总低频增益的提高,因此将引入相近的低频增益级极点,只有依靠Miller补偿电容的倍增效应可以实现主极点的压缩。因此,增益提高的Cascode与常规Cascode具有相类似的单位带宽表达式,但与两级增益的GBW明显不同。两级运放次极点为p2=gm2/CL,Cascode运放的次极点p2=gm2/Cx则明显扩展,其中由Cgs和Cgd组成的Cx电容远远小于负载电容CL。

在GBCA中,辅助运放Aadd的作用可视为对gm2管跨导的倍增,或是通过进一步改变Cascode的输出阻抗提高系统增益。在Aadd为理想常数且带宽无穷大的条件下,反馈放大器则不引入附加极点,导致GBCA运放低频增益进一步提高为

A0=gm1[(1+Aadd0)gm2]ro2ro1≈Aadd0gm1ro1gm2ro2 (10-58)

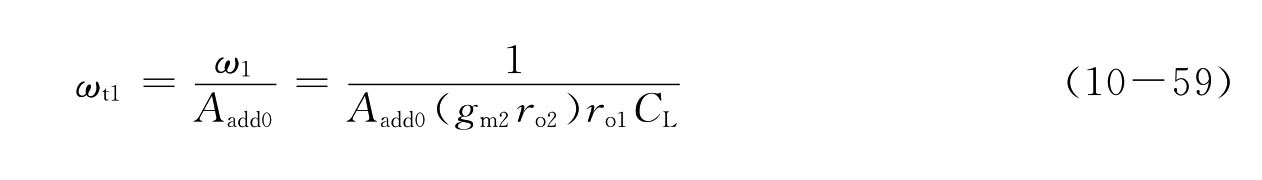

主极点压缩为

显然,GBCA运放系统的直流增益提高了Aadd0倍,抵消了主极点ωt1下降同样倍数的作用,使GBCA的单位增益带宽GBW仍然保持为原主运放ωu的结果不变,即

由于次极点频率ω2=(1+Aadd0)gm2/Cx在理想条件下可以扩展到极高频,因此不考虑辅助运放频率特性条件下的GBCA放大器退化成两极点系统,且次极点的作用可以忽略,理想GBCA保持单级增益的频率特性不变。在频率远大于ωt1但小于ω2的中频段,GBCA运放在理想状态下的频率特性可表示为

现实中,辅助放大器至少引入1个以上的极点。当反馈运放引入一个极点后,GBCA运放为3极点系统;当引入2个极点,则GBCA运放则为4级系统。显然,辅助运放引入极点形成的ωau若远高于ωu,则对主运放的影响可以忽略;否则,辅助运放低频极点的引入,将显著改变GBCA的中高频特性,并对系统的稳定性产生重要影响。

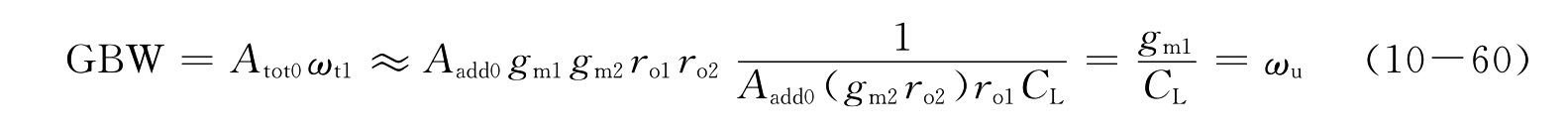

在GBCA中,存在一个由辅助放大器和M2源极跟随器构成的内部负反馈环路。在辅助运放单极点近似条件下,设ωa1和ωau分别为辅助运放的主极点频率和单位增益带宽,GBCA次极点频率ω2同时也成为内部环路的高频次极点,即该内部环路的次极点与主运放的次极点重合。为确保内部环路的稳定,内部环路单位增益带宽ωau只能位于环路的次极点范围内,即ωau<ω2,在此条件下辅助运放的主极点被压缩至ωa1《ω2的区域。

当ωa1》ω2>GBW时,对应于以上理想的GBCA状态,此时ω2成为内部环路的主极点,ωau由ω2决定,在ωa1次极点很大的条件下,环路稳定;否则,当ωa1较小使ωau>ω2时,则环路不稳定。实际上,由于低频极点ωa1>ω2的可能性几乎不存在,这里仅讨论有现实意义的ωa1《ω2状态,即ωau<ω2的内部闭环稳定控制状态。

在现实条件下,x结点输出阻抗受辅助运放的调节作用,使得次极点频率ω2与辅助运放的频率特性相关。由于在ω2频率下辅助运放的增益Aadd<1,则次极点频率保持ω2≈gm2/Cx,即原始CA的结果近似不变,且ω2》GBW。在高频下增益也会产生衰减。

由于辅助运放相对于基本原始运放的结构近似,ωa1>ωu的条件很难满足,若至少在ωt1的频率下辅助运放的增益应为低频常数,即ωa1>ωt1则可保持主极点位置和带宽不变。由于辅助运放的增益远小于系统增益,ωa1>ωt1的条件容易满足。对此条件两边同乘以一个Aadd0常数后,得到Aadd0ωa1=ωau、Aadd0ωt1=ω1。

辅助运放的单位增益带宽ωau必须大于基本Cascode运放的主极点频率ω1,即ωau>ω1,这是实现倍增控制的最低要求。当辅助运放也采用与基本运放相同的Cascode单级增益时,以上最低要求比较容易满足。由此得到ωau的范围为

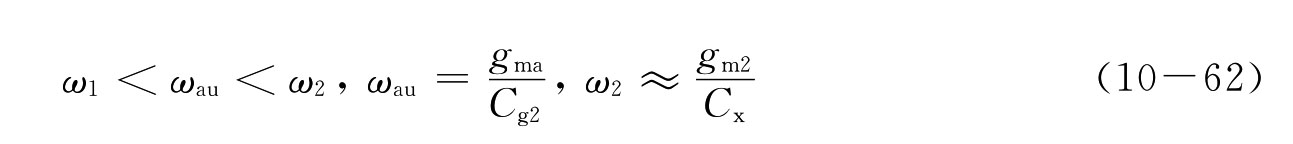

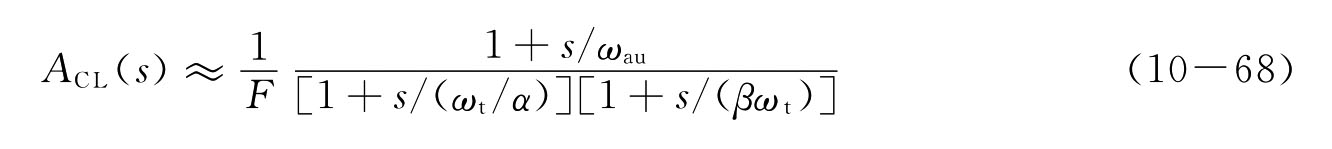

ωau可在其频率附近也就是系统GBW附近引入开环主运放的偶对。虽然偶对对运放系统的相位特性影响不大,但对瞬态特性在特定条件下的影响很大。首先,应考察辅助运放引起偶对的原因。在忽略寄生电容作用的条件下,单级点性质的GBCA增益传递函数为

若反相放大器Aadd(s)为常数A0,或其带宽远高于Atot带宽,则输出阻抗保持RO≈A0gm2ro1ro2常数不变,即与频率无关,形成主运放增益Atot的单极点频率为ωt1=1/(ROCL)=1/(A0gm2ro1ro2CL)。

若辅助运放采用Aadd(s)=-Aadd0/(1+s/ωa1)的单极点模型近似,且Aadd0》1,得到

代入ωau=Aadd0ωa1的条件,在ω》ωa1的频率范围下,开环增益为

![]()

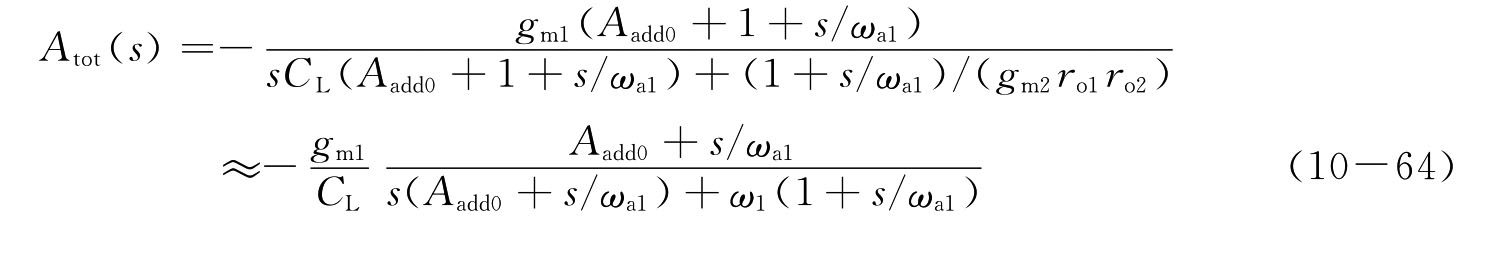

由内部反馈环路形成的一对偶对分别为ωdz=ωau、ωdp=ωau+ω1。以偶对中数值较小的零点ωdz为参照,偶对的分离系数α为

![]()

显然,α→1,该零极点的分离度与辅助运放的单位增益带宽和基本CA放大器主极点频率密切相关。在以上简单近似条件下,由于ωau与ω1无关,则当单调增加辅助运放带宽使ωau》ω1时,形成的偶对相互间越来越靠近,对系统相位的影响可以忽略,而对瞬态特性的影响必须以闭环系统进行分析。对于F反馈系数由以上开环构成的闭环系统,开环系统的偶对将变成闭环系统的偶对。在ωau》ω1的频率范围下,有

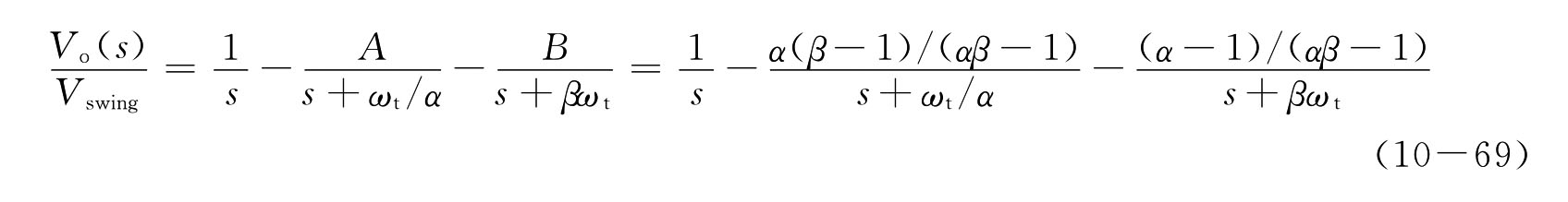

设闭环系统在主次极点分离条件下的主极点频率为ωt=Fωu。考虑到ωdp≈αωdz=αωau,且α→1;偶对中极点ωdp相对ωt的位置由比值系数β=ωdp/ωt决定,即主要由ωau与ωu的位置关系所决定,ωau=(β/α)ωt。则有

在阶跃激励下,对以上传递函数进行拉氏反变换,得到如下的输出形式:

在α→1的条件下,以上闭环系统在1(t)激励下的瞬态输出响应近似为

瞬态特性的理论分析表明,闭环偶对的相对位置关系近似保持原有开环下的性质不变。在高频极点影响下,闭环主极点带宽下降为ωt/α。当β>1时,即ωau>ωu,偶对在系统闭环带宽以外,对闭环瞬态特性的影响可忽略;当β<1,即ωau<ωu时,偶对在系统闭环带宽以内,将对系统闭环瞬态特性产生重要影响。设计中应取β》1,且α→1,辅助运放的单位增益带宽范围为满足系统稳定性和瞬态响应速度的要求,其合理的范围为(ωt/α~ω2)之间,即

因此,对于辅助运放的单极点近似,并在忽略高频次极点ω2的条件下,辅助运放的带宽选取大于闭环带宽ωt,但远小于ω2,使系统稳定性和瞬态响应特性均能很好地满足。

以上系统的双极点分析结果仅在ω2》GBW的条件下成立,因此当ωau增大到主运放的GBW以外时,若ωau仍然远离ω2,高频次极点的作用仍然可以忽略。否则,当ωau增加到超过GBW后并接近ω2时,ω2对系统的影响无法忽略,即这两个高频极点间的相互影响和作用导致共轭复极点产生,并向RHP平面移动。这样,原有的偶对消失,不但对闭环系统的瞬态特性产生明显的作用,并使闭环系统的稳定性下降。当继续增加ωau使ωau》ω2后,原来的偶极的性质恢复,并且位于ω2外的高频段,对系统影响逐步减弱,并还原到辅助运放不含极点或带宽无穷大时所对应的理想控制状态。

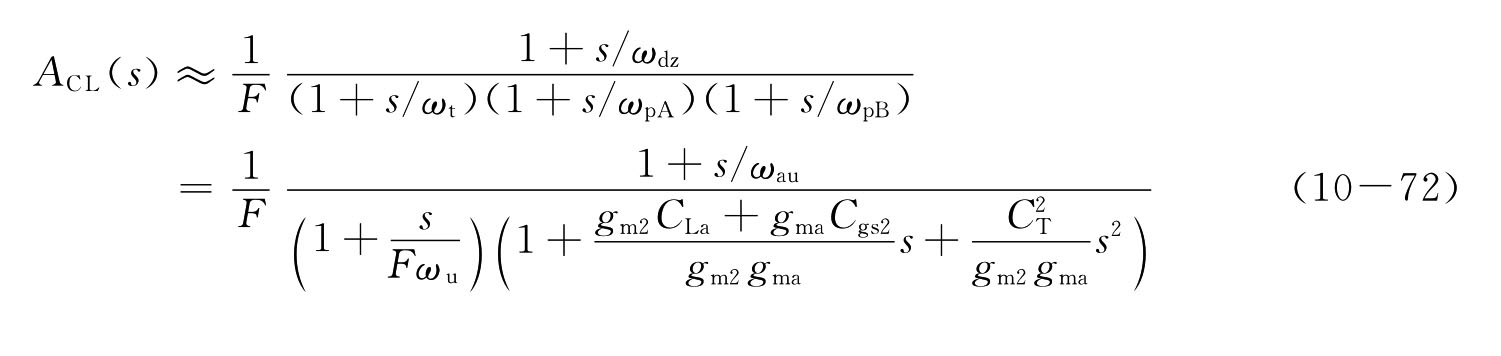

在ωt<ωau<ω2的条件下,考虑高频次极点影响后的闭环传递函数为

如辅助运放引入2个极点,则闭环系统极点总数达到4个,主极点和GBW的近似通常可以成立,在ωau附近有一对偶对,同时在辅助运放次极点附近也形成一个高频偶对,此外主运放还保留一个高频次极点频率。与三极点系统类似,随着ωau的增加偶对会发生变化。当低频偶对在系统带宽GBW以内时,对瞬态特性的影响不可忽略,在此区间内由于偶对中的零点和极点在两个特定的频率点下相交,α=1而使瞬态项抵消,但该频率点的精确控制无法实现。而当低频偶对增加到超过系统带宽并接近高频偶对时,原来两对偶对相互作用后将产生一对共轭复极点和一对共轭复零点,导致稳定性下降。通常在达到两对偶对相互作用之前,可实现最佳的瞬态响应控制。

在避免形成共轭复极点和共轭复零点的前提下,将系统中的所有极点均以系统带宽为参照进行归一化。保持主运放70°的相位裕度,则Cascode主运放次极点至少为2.6GBW,辅助运放形成的偶对对GBCA运放系统的相位迟滞影响可以忽略,则GBCA系统电路的相位裕度与Cascode主运放基本相同。辅助运放的单位增益带宽近似取大于系统GBW但小于主运放次极点,即ωau在1~1.5GBW之间,而辅助运放的次极点在5倍GBW外,该极点频率越高,瞬态响应速度越快,而且系统频率特性对ωau变化的敏感度越低。这要求辅助运放的相位裕度在80°以上,内部环路的相位裕度仍然保持在60°左右。

根据以上分析结果,得到GBCA电路的设计流程如下:

(1)根据系统应用要求,确定GBCA的系统结构和主要设计指标;

(2)根据噪声、精度、速度等核心指标要求,给出关键结点位置初始电路参数设计;

(3)估算电路内各结点负载电容和寄生电容的大小;

(4)根据速度要求和负载电容大小,计算充放电的尾电流值;

(5)根据采样周期,设定GBCA主运放电路的增益和带宽要求,即确定ω1,A0,GBW=A0ω1以及ω2,满足ω2>2.64GBW的要求;

(6)确定辅助运放的增益和带宽,即确定Aadd0、ωa1、ωa2,满足ωau=Aaddωa10=1.2GBW、ωa2>5GBW的要求;

(7)根据带宽、增益和速度等关键指标的计算结果,设计电路中各MOS管的尺寸,修正对寄生电容的结算结果;

(8)结合实际CMOS工艺,采用HSPICE或Spectre模拟,验证并修改设计结果。