5.3.4 较复杂电路的原理图设计

本节通过一个2位十进制数字频率计的设计过程来介绍原理图输入法设计较复杂逻辑电路的方法。

1)频率计测频原理

频率计是能够测量和显示信号频率的电路。所谓频率,就是周期性信号在单位时间内变化的次数。首先给出具有固定宽度T的方波脉冲做门控制信号,时间基准T称为闸门时间。宽度为T的方波脉冲控制闸门的一个输入端,被测信号控制闸门另一输入端。当门控制电路的信号到后,闸门开启,于是输出端产生脉冲信号到计数器,计数器开始工作,直到门控信号结束,闸门关闭,计数器停止计数。同时,锁存器产生一个锁存信号输送到锁存器的使能端将结果锁存,并把锁存结果输送到译码器来控制七段显示器,这样就可以得到被测信号的数字显示的频率。而在锁存信号的下降沿到来时,逻辑控制电路产生一个清零信号将计数器清零,为下一次测量做准备,实现了可重复使用。

因此该频率计可由闸门电路,2位十进制计数器,显示电路3部分组成。整个设计可以划分为2个层次,即将闸门电路和两位十进制计数器作为底层模块分别设计,由于显示电路比较简单,可将该电路直接置于频率计电路的顶层主体电路设计中。

2)闸门电路模块设计

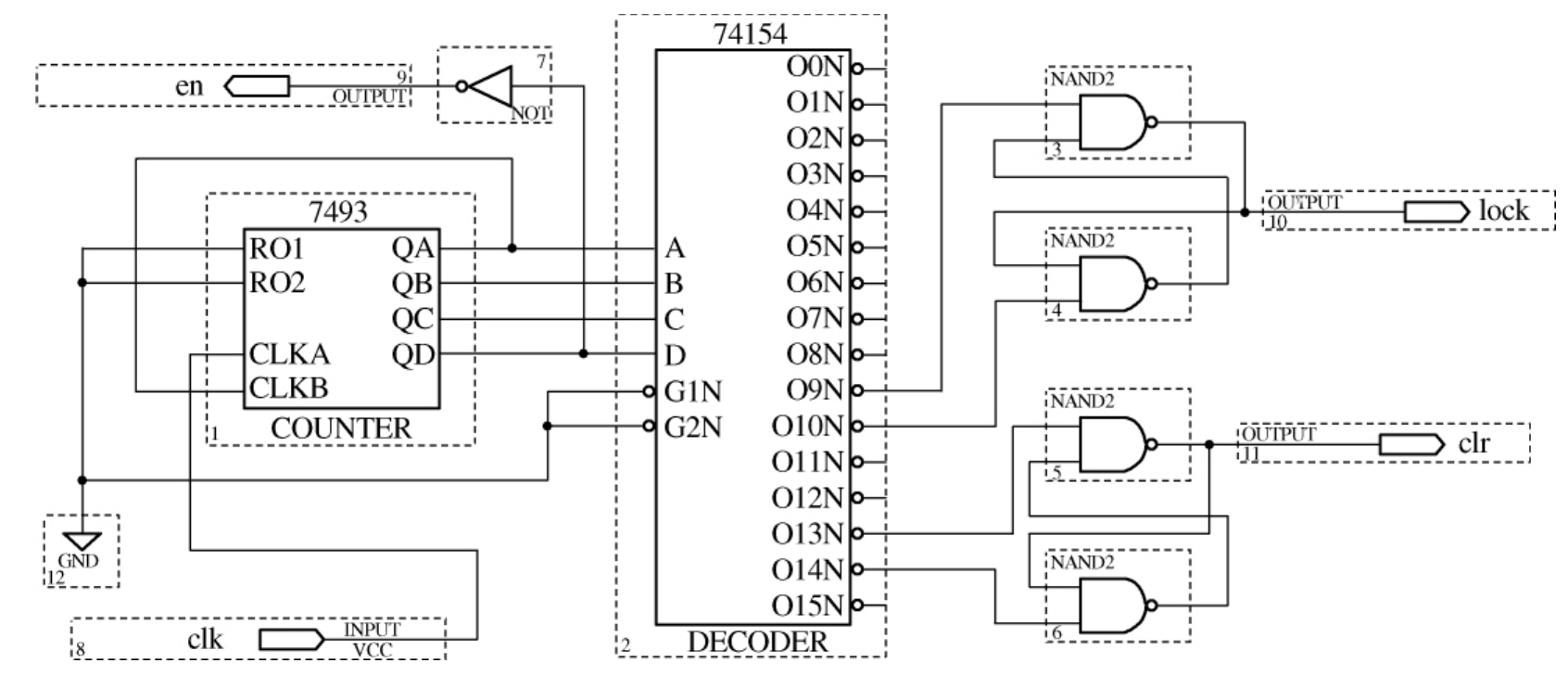

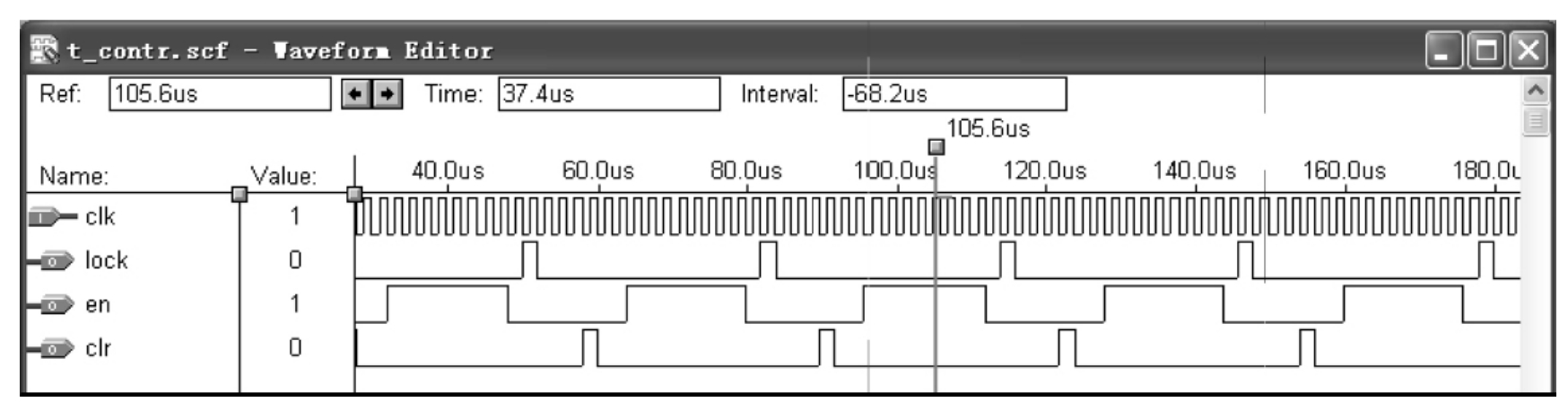

频率计电路工作时先要产生一个计数允许信号(即闸门信号),在闸门信号有效时间内,对被测信号计数,即为信号的频率。因此频率计能顺利完成测频需要三个控制信号:计数使能信号en、锁存信号lock和清零信号clr,根据三个控制信号时序要求,图5.38给处了相应电路,设该电路的文件名为t_contr.gdf。仿真波形如图5.39所示,观察仿真结果可知,使能信号en、锁存信号lock和清零信号clr满足设计要求,因此仿真结果正确。在仿真结果正确无误后,将设计的闸门电路包装成一个元件入库,元件名为t_contr。

图5.38 闸门电路原理图

图5.39 闸门电路仿真波形

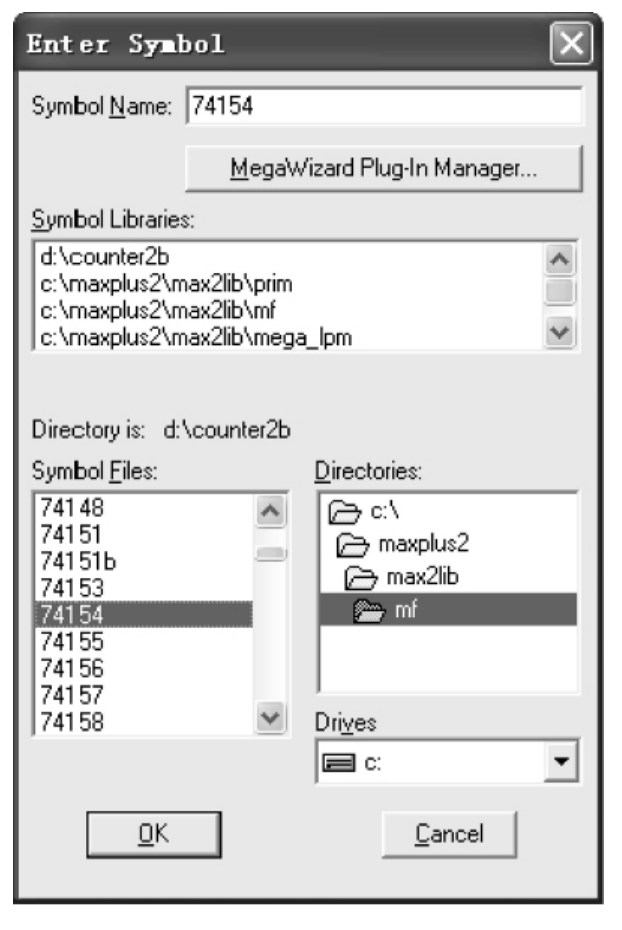

图5.40 调出元件74154

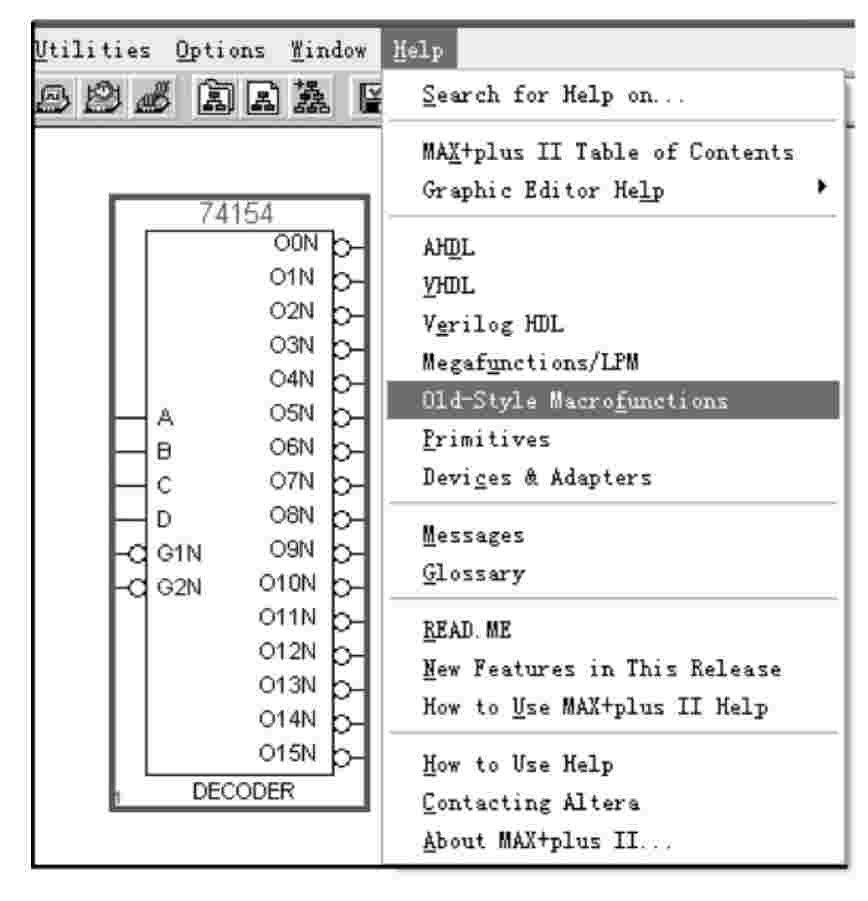

图5.41 从Help中了解74154的详细功能

74系列的元件在c:\maxplus2\max2lib\mf宏功能元件库中(见图5.40),74系列器件的详细功能及其逻辑真值表可以通过查阅“Help”菜单来获得,选择“Help”→“Old-Style Macrofunctions”(见图5.41),然后选择Counters选项。

3)位十进制计数器的设计

(1)设计原理

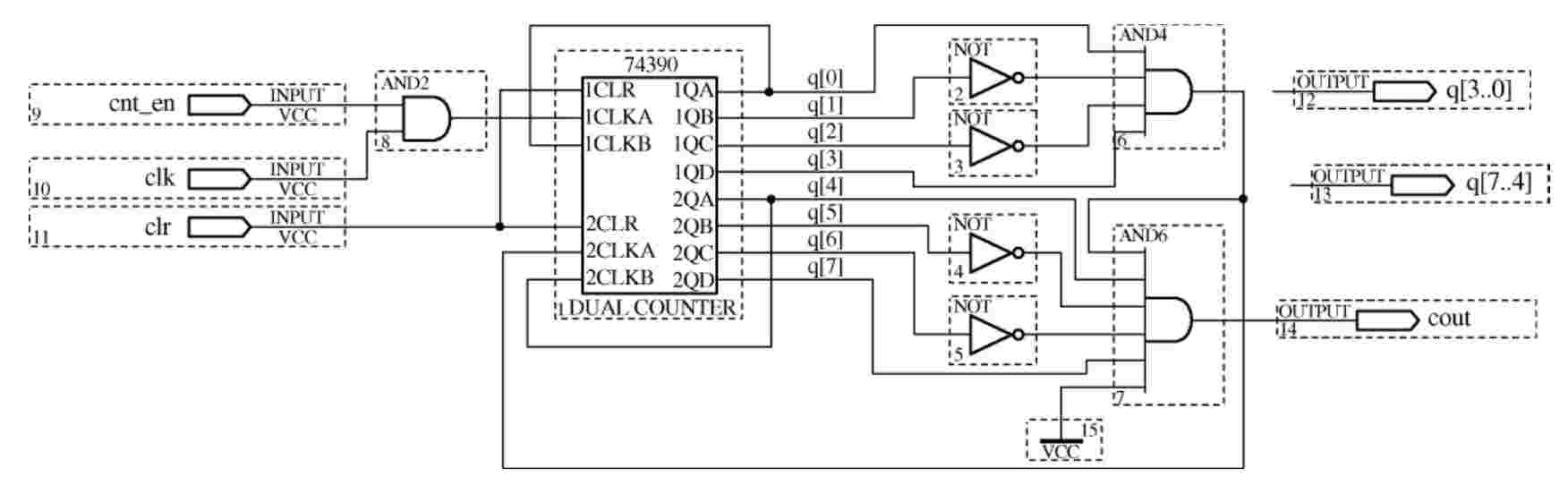

2位十进制计数器可以用一个双十进制计数器74390和其他一些辅助元件来完成。电路原理图如图5.42所示,图中74390连接成两个独立的十进制计数器,待测频率信号clk通过一个与门进入74390的计数器1的时钟输入端1CLKA,与门的另一端由计数使能信号cnt_en控制(当cnt_en=‘1’时允许计数;cnt_en=‘0’时禁止计数)。计数器1的4位输出q[3]、q[2]、q[1]和q[0]并成总线表达方式即q[3..0],由OUTPUT输出端口向外输出计数值,同时由一个4输入与门和两个反向器构成进位信号进入第二个计数器的时钟输入端2 CLKA。第二个计数器的4位输出q[7]、q[6]、q[5]和q[4]也并成总线表达方式q[7..4],由OUTPUT输出端口向外输出计数值。这两个计数器的总的进位信号即扩展进位信号,由一个六输入与门和两个方向器产生,由cout输出。clr是计数器的清零信号。

图5.42 2位十进制计数器原理图

(2)计数器原理图实现

向原理图中调入所需要的元件,此原理图用到了总线表达方式,若要将一根细线变成以粗线显示的总线,可以先将其单击,使其变红,再点击右键出现快捷菜单,选择Line Style中的第2项,或者选菜单“Option”→“Line Style”;若在某线上加信号标号,也应该在该线某处单击使其变红,然后键入标号名称;标有相同标号的线段可视作连接线段,可不必再连接。保存原理图,保存文件名为2_counter.gdf。

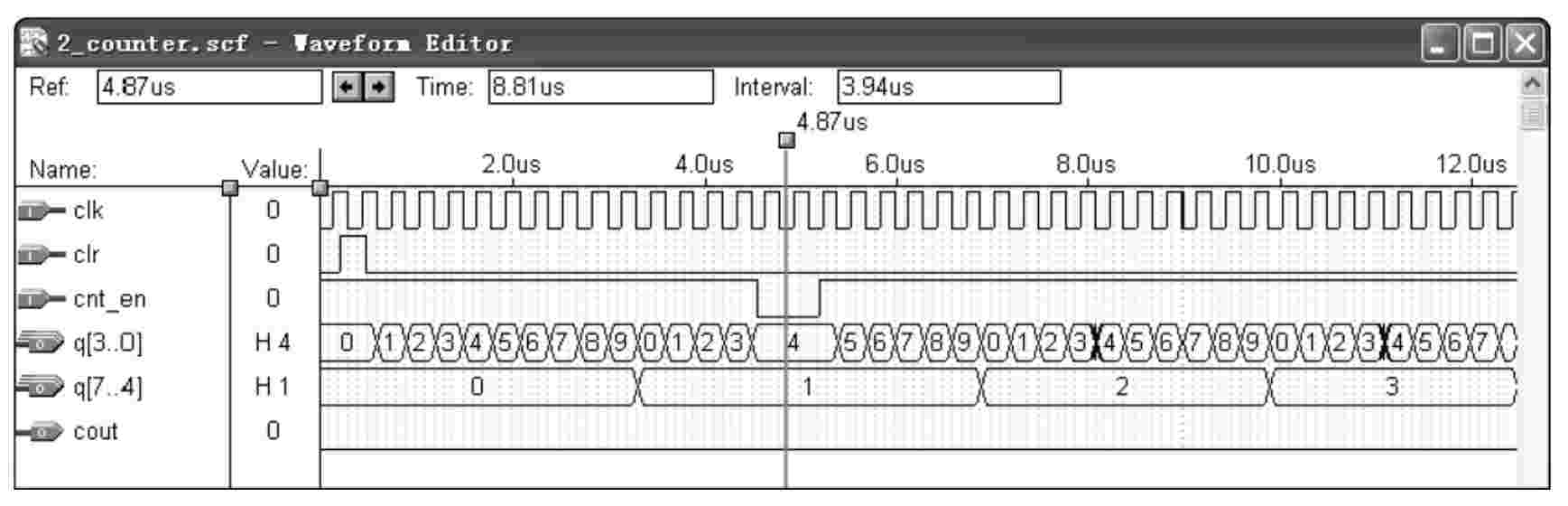

(3)波形仿真

由波形图5.43可见,图5.42电路的功能完全复合原设计要求:当clk输入时钟信号时,clr具有清零功能,当cnt_en位高电平时允许计数,低电平时禁止计数,当低4位计数器计到9时向高4位进位。

(4)包装入库

将此项设计包装成一个元件存入库中以备后用,原理图的文件名为2_counter.gdf,因此电路对应的元件名为2_counter。

图5.43 2位十进制计数器的仿真波形

4)频率计电路顶层原理图设计

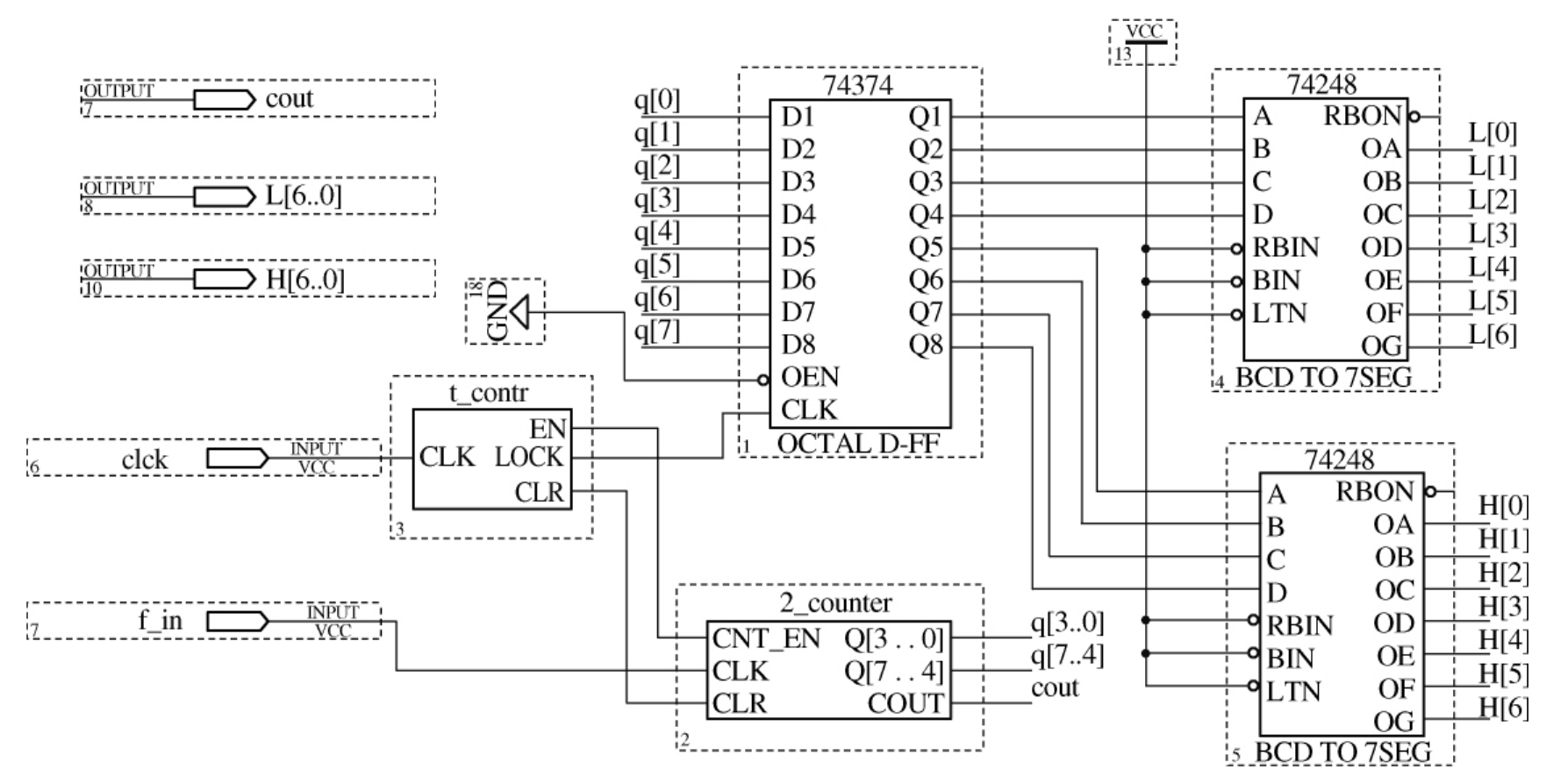

在成功完成底层单元电路模块设计仿真后,可根据测频原理,完成图5.44所示的频率计电路顶层原理图的设计文件。

图5.44中t_contr和2_counter为前面设计的底层单元电路模块,74374是8位数据寄存器,用于寄存输出2_counter的个位和十位计数值q[3..0]和q[7..4],其7位译码输出L [6..0]和H[6..0]可直接与七段共阴极数码管相连,L[6..0]将显示个位频率计数值,H [6..0]将显示十位频率计数值;clck为系统基准输入信号,f_in为待测频率信号,cout为进位扩展信号,用于频率计扩展。

图5.44 频率计电路顶层原理图

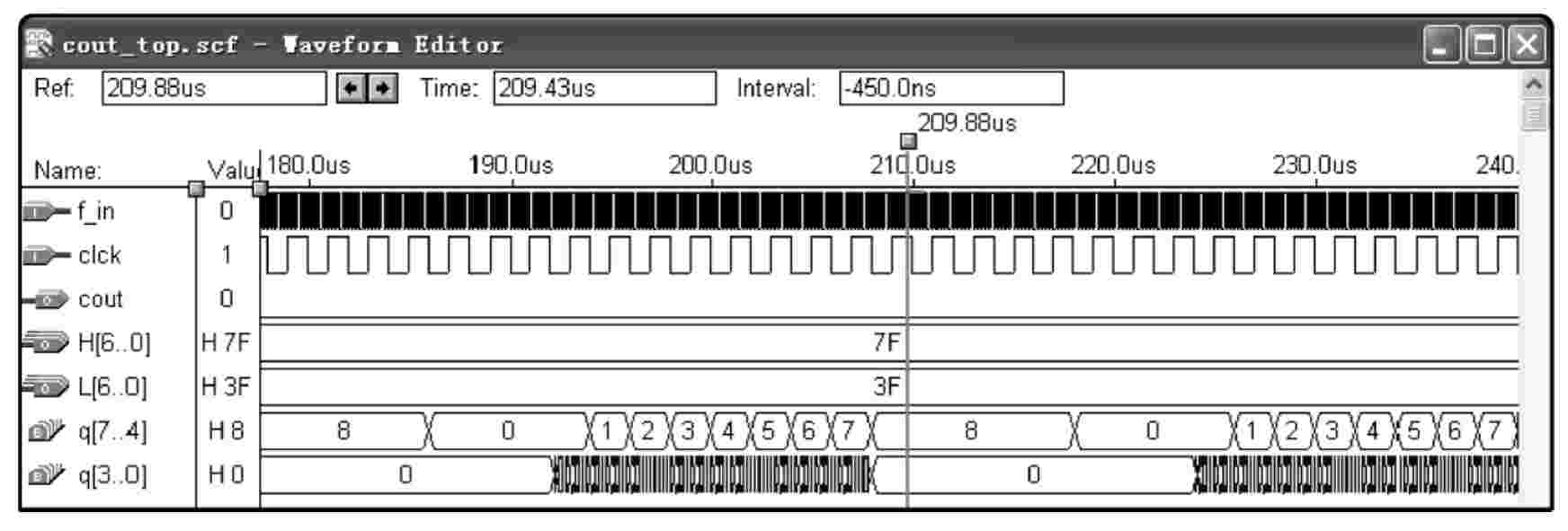

图5.45是频率计电路顶层原理图的仿真波形,由图可知:测频计数器中的计数值q [3..0]和q[7..4]随着f_in的脉冲的输入而不断发生变化,但由于74373的锁存器功能,两个74248输出的测频结果,L[6..0]和H[6..0]始终分别稳定在“7F”和“3F”上,通过七段显示数码管,此二数分别显示8和0。

图5.45 频率计电路仿真波形