.jpg)

4.4.3 动态随机存取存储器(DRAM)

静态RAM的最大优点是几乎不需附加的控制电路就可和大多数CPU或系统总线直接相连,它的存取速度快。但静态RAM的基本存储单元需6个MOS管,因此集成度低,每位的制造成本高,价格也就较高。

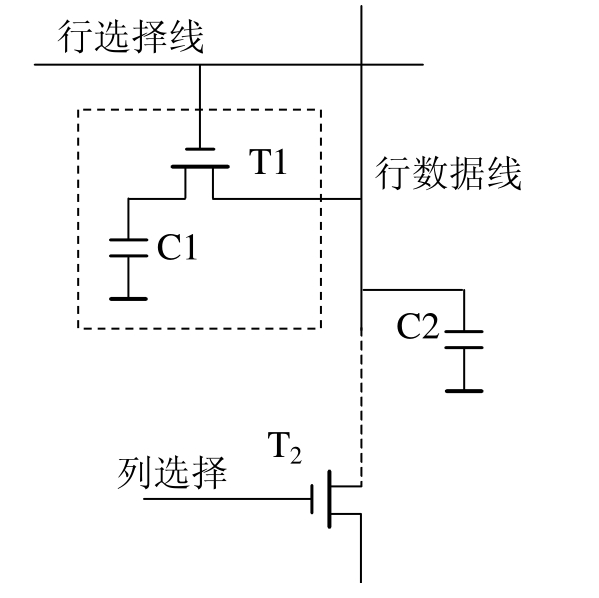

1.单管动态基本单元电路

如图4.11所示是动态RAM的一种基本存储结构。T1和极间电容C1构成一个基本存储单元,用C1上有无电荷表示存1或存0。图4.11中T2为列选通管,为同处一列的基本存储单元所公用。C2是数据线的分布电容,一般C2>C1。

(1)信息写入

当要进行信息写入时,使行选择线和列选择线为高,T1、T2为导通状态。若写1,使数据线为高,C1充电,有电荷;若写0,使数据线为低,C1不充电或放电,C1无电荷。

(2)信息读出

读出所存储信息时,使行选择线和列选择线为高,T1、T2为导通状态。C1的信息经Tl和T2传至数据线,即在数据线上可直接获取所存储信息。由于C1很小(约0.1~0.2 pF),读出信号(0.2 V左右)需进行放大。

图4.11 单管动态存储器单元电路

此外,由于C2的存在,并且C2>C1,因此每次读出信息后,原存储信息被破坏了(C2向C1充电,使0变成l;或C1向C2放电,使1变成0),即这种读出为破坏性读出。为了保持原存储信息不变,必须在读出后进行信息再生。再考虑到读出信号需进行放大,所以一般在DRAM内部要设置读出再生放大电路。

(3)定时刷新

动态RAM的基本存储单元是靠电容上有无电荷来表示存l或存0的。虽然MOS管是一种高阻抗器件,但不可能将阻抗做到无穷大,因此C1上电荷经过一段时间就会泄漏掉(一般为几毫秒到几十毫秒),信息不能长期保存。所以要周期性地进行信息重新写入,即在其所存储信息未发生质的变化之前,再重新写入一次,这称为动态RAM的刷新。读出再生放大电路也用于动态存储器的刷新操作。

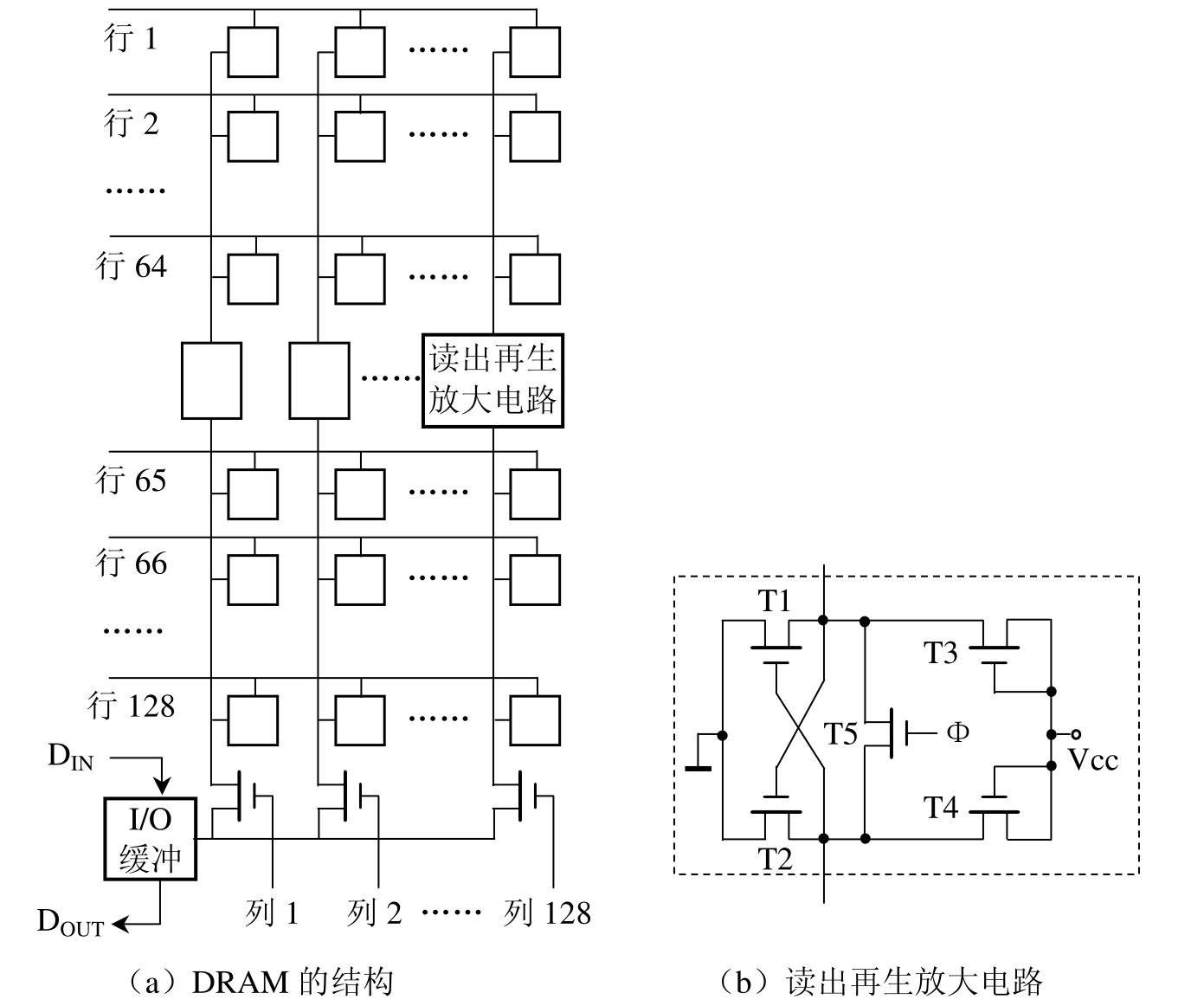

2.动态RAM的电路结构

图4.12(a)是一种动态RAM的结构示意图。该电路为复合译码的“×l”位结构,由128行和128列组成一个存储矩阵。图4.12(a)的中间有128个方框,表示128个读出再生放大电路,每个电路负责一列,共128个基本存储单元,这些单元平衡配置在读出再生放大电路的两侧,每侧各有64个。

图4.12 DRAM的结构

如图4.12(b)所示是读出再生放大电路,其核心是一个双稳态触发器,由Tl~T4组成。与六管静态RAM基本单元中相类似,T3和T4等效于电阻。电路中增加了T5管进行预充电控制。读/写操作前,T5导通,触发器及其周围电路处在平衡状态。在读/写及刷新操作时,T5关断,处理依赖于以下具体操作:

(1)写操作

写操作时相应的行、列选通管导通;外部数据将先对读出再生放大电路建立起稳定的状态(1或0),然后再由它对选中单元完成写入。需要指出,同一写入数据,当它写到读出再生放大电路上方或下方的单元时,其存储状态正好相反;但这并不要紧,因为读出总是从该电路的一端进行,所以数据在读出时又会与写入时一致。

(2)读操作

读操作时相应的行、列选通管导通,从选中单元中读出的信息,先使读出再生放大电路建立起稳定状态,该状态一方面向数据线输出,另一方面又对存储单元进行刷新。

(3)刷新

刷新有多种方法,但通常采用“仅行地址有效”的方法。此时,由外部提供有效行地址,选中相应一行;同时使列地址无效,即关闭所有的列选通管。这样,该行上所有128个存储单元中的数据将在内部读出,经过同一列上读出再生放大电路的刷新放大而得到加强。由于所有的列选通管均处于关闭状态,数据并不输出到存储器的外部。

实际上,读、写操作也具有刷新一行基本单元的功能。但由于操作时其行地址无规律性,加上列选通并驱动数据使消耗功率增大,所以不能用于刷新目的。刷新需由刷新控制器(一些新型动态RAM芯片已将其做在内部)控制。刷新控制器中的刷新计数器按照一定的时钟频率进行行地址计数,保证在一定的时间间隔内所有的行都能刷新一遍。显然,动态存储器的刷新应周期性重复进行。

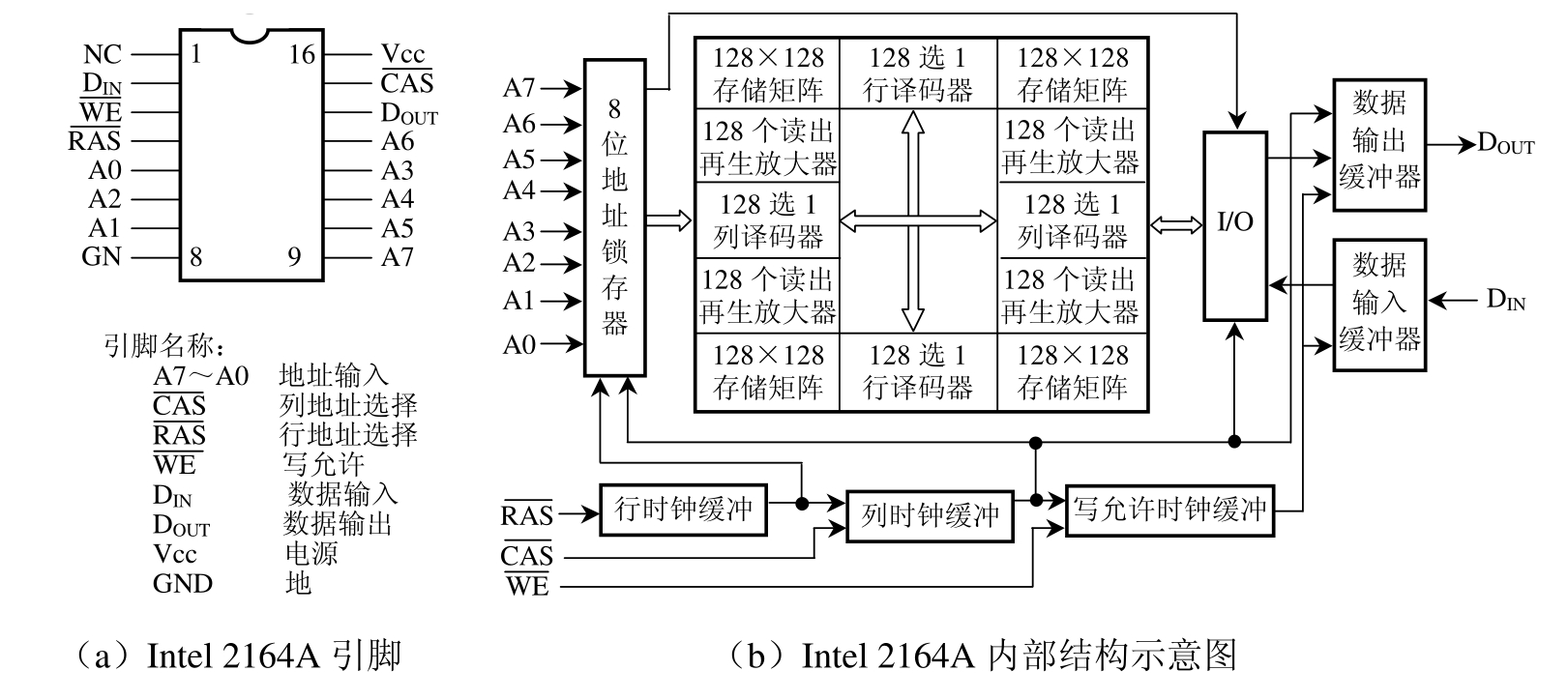

3.动态RAM芯片举例

与静态RAM一样,了解动态RAM芯片的原理还是以早期的小容量芯片为宜,在此选择Intel公司的2164A。Intel 2164A为64 K×1位存储芯片,16个引脚,采用DIP封装。其引脚如图4.13(a)所示。

Intel 2164A只有8条地址线A7~A0,而按它的存储容量,片内寻址应使用16位地址线。这里是采用了地址线复用技术,地址线只安排了一半。使用时,地址分时进行传送:先送8位(称为行地址),再送8位(称为列地址)。为此,Intel 2164A设置了两个引脚,用来分别输入行地址选通信号 (Row Address Strobe)和列地址选通信号

(Row Address Strobe)和列地址选通信号 (Column Address Strobe)。

(Column Address Strobe)。

图4.13 Intel 2164A引脚和内部结构示意图

在Intel 2164A的内部设有行地址锁存器和列地址锁存器。作为“×1位”芯片,Intel 2164A采用了DIN和DOUT两条数据线,这是为了对输入数据和输出数据分别进行缓冲。在使用时,这两个引脚在外部连接在一起,连接到CPU 或系统数据总线的某一位。

与Intel 2114静态RAM一样,Intel 2164A没有设置读信号,只设置了写信号引脚 。为了减少芯片的外部引脚,Intel 2164A没有设置片选信号,而由行地址选通信号

。为了减少芯片的外部引脚,Intel 2164A没有设置片选信号,而由行地址选通信号 兼作片选。这样,当

兼作片选。这样,当 同时有效时,表示进行写操作;当

同时有效时,表示进行写操作;当 无效而

无效而 有效时,表示进行读操作(或当

有效时,表示进行读操作(或当 无效时,

无效时, 兼作读信号)。由于刷新是按行进行,所以刷新时只需

兼作读信号)。由于刷新是按行进行,所以刷新时只需 有效。可见,在Intel 2164A中

有效。可见,在Intel 2164A中 有3个作用:

有3个作用:

(1)正常读/写时,进行行地址选通,将行地址送入到行地址锁存器;

(2)在刷新时,进行刷新行地址选通;

(3)兼作片选信号。

Intel 2164A的内部结构如图4.13(b)所示。它设有4个128×128存储矩阵、2套128选1行译码器、2套128选1列译码器和4组读出再生放大器(每组有128个读出再生放大器)。实际上,图中的每一个128×128存储矩阵以及相应的一组读出再生放大电路就是如图4.12(a)所示的电路,即Intel 2164A内部有4套如图4.12(a)所示的电路。

当给定一个16位地址时,行地址的低7位(RA6~RA0)从每个存储矩阵中选择一行,列地址的低7位(CA6~CA0)从每个存储矩阵中选择一列,每个存储矩阵中被选择的行和被选择的列交汇处的单元被选中,最后由4选1 的I/O门从4个矩阵的被选单元中选定一个(由RA7和CA7控制),进行读或写。

由于行地址和列地址需分时送入以及需要进行刷新操作等,动态RAM的时序特性要比静态RAM复杂。对Intel 2164A的时序可分读周期、写周期、读-修改-写周期、刷新周期和页模式操作五个。

上一篇:复合空间理论

下一篇:工程项目的投资及构成